- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384755 > MT48LC64M4A2 (Micron Technology, Inc.) SYNCHRONOUS DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | MT48LC64M4A2 |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | SYNCHRONOUS DRAM |

| 中文描述: | 同步DRAM |

| 文件頁數(shù): | 45/62頁 |

| 文件大?。?/td> | 1517K |

| 代理商: | MT48LC64M4A2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

45

256Mb: x4, x8, x16 SDRAM

256MSDRAM_E.p65

–

Rev. E; Pub. 3/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2002, Micron Technology, Inc.

256Mb: x4, x8, x16

SDRAM

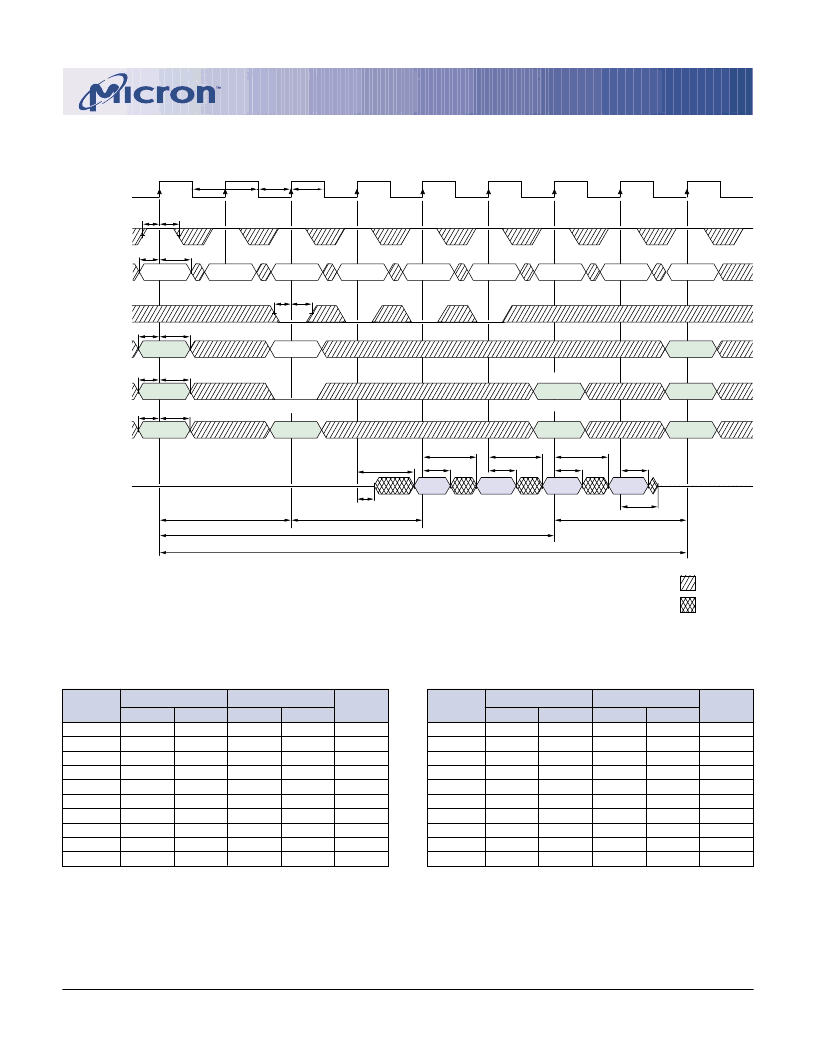

READ – WITHOUT AUTO PRECHARGE

1

ALL BANKS

tCH

tCL

tCK

tAC

tLZ

tRP

tRAS

tRC

tRCD

CAS Latency

DQM/

DQML, DQMU

CKE

CLK

A0-A9, A11, A12

DQ

BA0, BA1

A10

tOH

D

OUT

m

tCMH

tCMS

tAH

tAS

tAH

tAS

tAH

tAS

ROW

ROW

BANK

BANK

BANK

ROW

ROW

BANK

tHZ

tOH

D

OUT

m

+ 3

tAC

tOH

tAC

tOH

tAC

D

OUT

m

+ 2

D

OUT

m

+ 1

COMMAND

tCMH

tCMS

PRECHARGE

NOP

NOP

NOP

ACTIVE

NOP

READ

NOP

ACTIVE

DISABLE AUTO PRECHARGE

SINGLE BANK

DON

’

T CARE

UNDEFINED

tCKH

tCKS

COLUMN

m

2

T0

T1

T2

T4

T3

T5

T6

T7

T8

NOTE:

1. For this example, the burst length = 4, the CAS latency = 2, and the READ burst is followed by a

“

manual

”

PRECHARGE.

2. x16: A9, A11, and A12 =

“

Don

’

t Care

”

x8: A11 and A12 =

“

Don

’

t Care

”

x4: A12 =

“

Don

’

t Care

”

*CAS latency indicated in parentheses.

-7E

-75

SYMBOL*

t

CMH

t

CMS

t

HZ (3)

t

HZ (2)

t

LZ

t

OH

t

RAS

t

RC

t

RCD

t

RP

MIN

0.8

1.5

MAX

MIN

0.8

1.5

MAX

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

5.4

5.4

5.4

6

1

3

37

60

20

15

1

3

44

66

20

20

120,000

120,000

TIMING PARAMETERS

-7E

-75

SYMBOL*

t

AC (3)

t

AC (2)

t

AH

t

AS

t

CH

t

CL

t

CK (3)

t

CK (2)

t

CKH

t

CKS

MIN

MAX

5.4

5.4

MIN

MAX

5.4

6

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

0.8

1.5

2.5

2.5

7

7.5

0.8

1.5

0.8

1.5

2.5

2.5

7.5

10

0.8

1.5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT48LC4M32B2 | SYNCHRONOUS DRAM |

| MT48LC4M32LFFC | SYNCHRONOUS DRAM |

| MT48LC64M8A2 | SYNCHRONOUS DRAM |

| MT48LC32M16A2 | SYNCHRONOUS DRAM |

| MT48LC8M16A2FB-75LIT | SYNCHRONOUS DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT48LC64M4A2_03 | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SYNCHRONOUS DRAM 256Mb: x4, x8, x16 SDRAM |

| MT48LC64M4A2_99 | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:Synchronous DRAM 256Mb: x4, x8, x16 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。