- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383632 > mPD705101 (NEC Corp.) V831TM 32-BIT MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | mPD705101 |

| 廠(chǎng)商: | NEC Corp. |

| 英文描述: | V831TM 32-BIT MICROPROCESSOR |

| 中文描述: | V831TM 32位微處理器 |

| 文件頁(yè)數(shù): | 40/72頁(yè) |

| 文件大?。?/td> | 302K |

| 代理商: | MPD705101 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

μ

PD705101

40

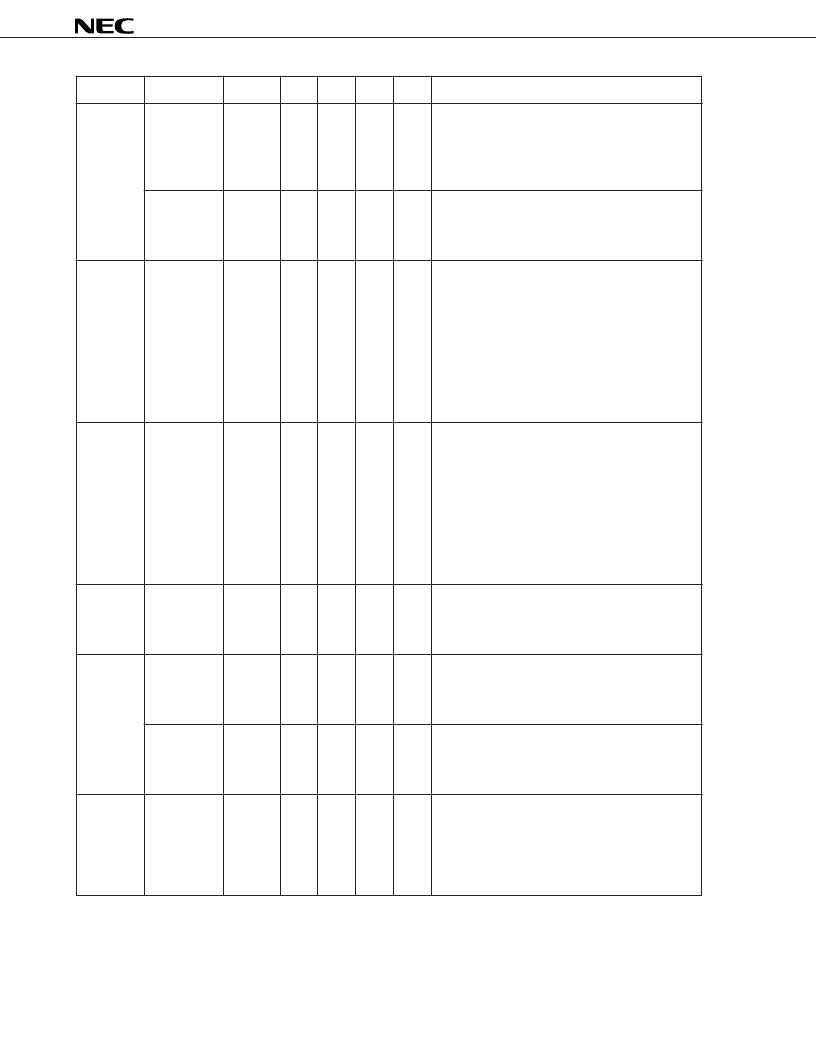

Instruction

Operand(s)

Format

CY

OV

S

Z

Function

SAR

reg1 ,reg2

I

0

Arithmetic right shift. reg2 is arithmetically

shifted to the right by the displacement

specified by the low-order five bits of reg1

(MSB value is copied to the MSB in sequence).

The result is written into reg2.

imm5, reg2

II

0

Arithmetic right shift. reg2 is arithmetically

shifted to the right by the displacement specified

by imm5, zero-extended to a word. The result is

written into reg2.

SATADD3

reg1, reg2,

reg3

VIII

Saturatable addition. reg1 and reg2 are added

together as signed integers.

[If no overflow has occurred:]

The result is written into reg3.

[If an overflow has occurred:]

The SAT bit is set. If the result is positive,

the positive maximum is written into reg3; if

the result is negative, the negative maximum

is written into reg3.

SATSUB3

reg1, reg2,

reg3

VIII

Saturatable subtraction. reg1 is subtracted from

reg2 as signed integers.

[If no overflow has occurred:]

The result is written into reg3.

[If an overflow has occurred:]

The SAT bit is set. If the result is positive,

the positive maximum is written into reg3; if

the result is negative, the negative maximum

is written into reg3.

SETF

imm5, reg2

II

–

–

–

–

Set flag condition. reg2 is set to 1 if the

condition specified by the low-order four bits of

imm5 matches the condition flag; otherwise it is

set to 0.

SHL

reg1, reg2

I

0

Logical left shift. reg2 is logically shifted to the

left (0 is put on the LSB) by the displacement

specified by the low-order five bits of reg1. The

result is written into reg2.

imm5, reg2

II

0

Logical left shift. reg2 is logically shifted to the

left by the displacement specified by imm5,

zero-extended to a word. The result is written

into reg2.

SHLD3

reg1, reg2,

reg3

VIII

–

–

–

–

Left shift of concatenation. The 64 bits

consisting of reg3 (high order) and reg2

(low order) are logically shifted to the left by the

displacement specified by the low-order five bits

of reg1. The high-order 32 bits of the result are

written into reg3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| mPD705101GM-100-8ED | V831TM 32-BIT MICROPROCESSOR |

| mPD784037 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| mPD784031 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| mPD784035 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| mPD784036 | 16/8-BIT SINGLE-CHIP MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPD705101GM-100-8ED | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:V831TM 32-BIT MICROPROCESSOR |

| MP-D70P-100/240V | 制造商:Panasonic Electric Works 功能描述: |

| MPD784031 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| MPD784035 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:16/8-BIT SINGLE-CHIP MICROCONTROLLER |

| MPD784036 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:16/8-BIT SINGLE-CHIP MICROCONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。