- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄102741 > MCIMX31VMN5CR2 (FREESCALE SEMICONDUCTOR INC) 532 MHz, MICROPROCESSOR, PBGA473 PDF資料下載

參數(shù)資料

| 型號: | MCIMX31VMN5CR2 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 532 MHz, MICROPROCESSOR, PBGA473 |

| 封裝: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, MAPBGA-473 |

| 文件頁數(shù): | 105/122頁 |

| 文件大小: | 1418K |

| 代理商: | MCIMX31VMN5CR2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁當(dāng)前第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁

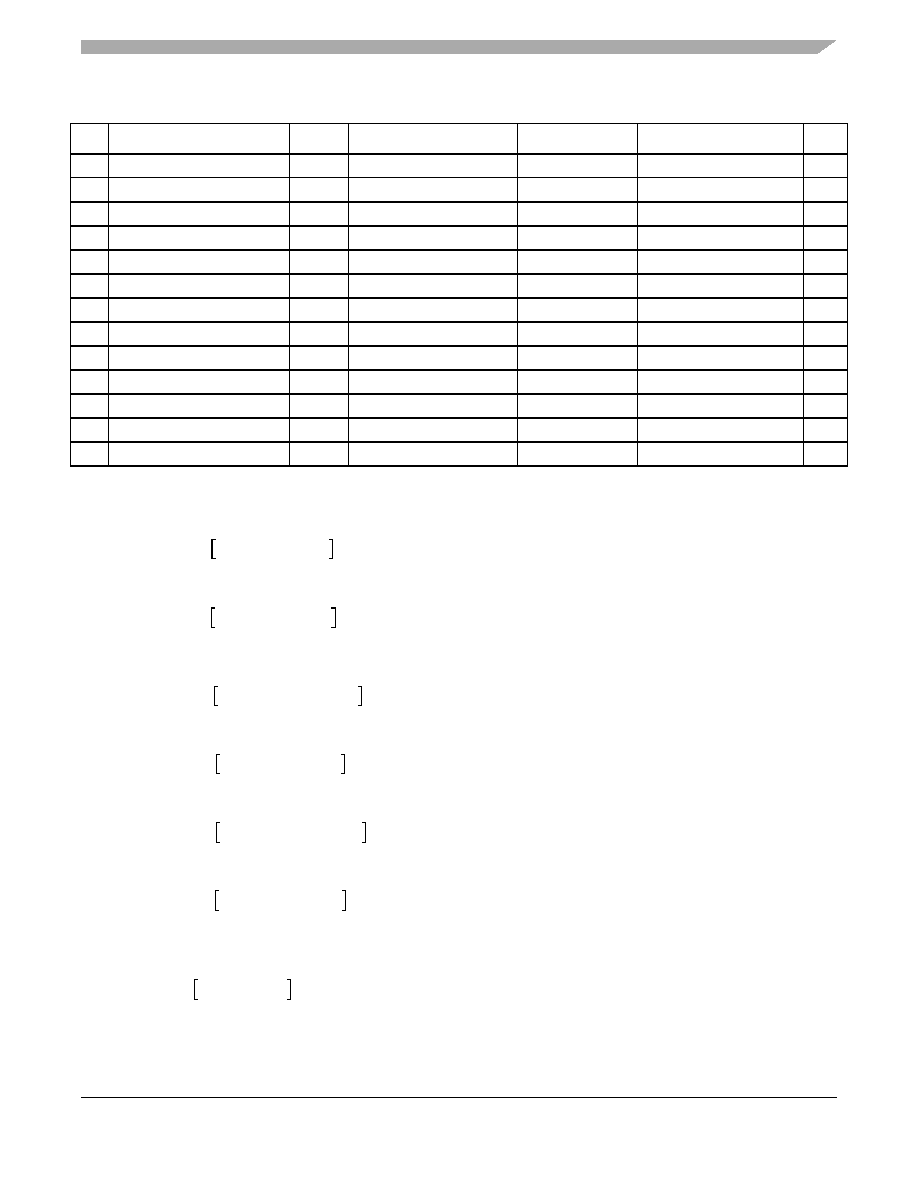

Electrical Characteristics

MCIMX31/MCIMX31L Technical Data, Rev. 4.1

Freescale Semiconductor

83

IP56 Controls setup time for write

Tdcsw

Tdicuw–1.5

Tdicuw

—

ns

IP57 Controls hold time for write

Tdchw

Tdicpw–Tdicdw–1.5

Tdicpw–Tdicdw

—

ns

IP58 Slave device data delay8

Tracc

0

—

Tdrp9–Tlbd10–Tdicur–1.5

ns

IP59 Slave device data hold time8

Troh

Tdrp–Tlbd–Tdicdr+1.5

—

Tdicpr–Tdicdr–1.5

ns

IP60 Write data setup time

Tds

Tdicdw–1.5

Tdicdw

—

ns

IP61 Write data hold time

Tdh

Tdicpw–Tdicdw–1.5

Tdicpw–Tdicdw

—

ns

IP62 Read period2

Tdicpr

Tdicpr–1.5

Tdicpr

Tdicpr+1.5

ns

IP63 Write period3

Tdicpw

Tdicpw–1.5

Tdicpw

Tdicpw+1.5

ns

IP64 Read down time4

Tdicdr

Tdicdr–1.5

Tdicdr

Tdicdr+1.5

ns

IP65 Read up time5

Tdicur

Tdicur–1.5

Tdicur

Tdicur+1.5

ns

IP66 Write down time6

Tdicdw

Tdicdw–1.5

Tdicdw

Tdicdw+1.5

ns

IP67 Write up time7

Tdicuw

Tdicuw–1.5

Tdicuw

Tdicuw+1.5

ns

IP68 Read time point9

Tdrp

Tdrp–1.5

Tdrp

Tdrp+1.5

ns

1 The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These

conditions may be device specific.

2 Display interface clock period value for read:

3 Display interface clock period value for write:

4 Display interface clock down time for read:

5 Display interface clock up time for read:

6 Display interface clock down time for write:

7 Display interface clock up time for write:

8 This parameter is a requirement to the display connected to the IPU.

9 Data read point:

10 Loopback delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a

device-level output delay, board delays, a device-level input delay, an IPU input delay. This value is device specific.

Table 51. Asynchronous Serial Interface Timing Parameters—Access Level (continued)

ID

Parameter

Symbol

Min.

Typ.1

Max.

Units

Tdicpr

T

HSP_CLK

ceil

DISP#_IF_CLK_PER_RD

HSP_CLK_PERIOD

----------------------------------------------------------------

=

Tdicpw

T

HSP_CLK

ceil

DISP#_IF_CLK_PER_WR

HSP_CLK_PERIOD

------------------------------------------------------------------

=

Tdicdr

1

2

--- T

HSP_CLK

ceil

2 DISP#_IF_CLK_DOWN_RD

HSP_CLK_PERIOD

-------------------------------------------------------------------------------

=

Tdicur

1

2

---T

HSP_CLK

ceil

2 DISP#_IF_CLK_UP_RD

HSP_CLK_PERIOD

--------------------------------------------------------------------

=

Tdicdw

1

2

--- T

HSP_CLK

ceil

2 DISP#_IF_CLK_DOWN_WR

HSP_CLK_PERIOD

---------------------------------------------------------------------------------

=

Tdicuw

1

2

---T

HSP_CLK

ceil

2 DISP#_IF_CLK_UP_WR

HSP_CLK_PERIOD

----------------------------------------------------------------------

=

Tdrp

T

HSP_CLK

ceil

DISP#_READ_EN

HSP_CLK_PERIOD

--------------------------------------------------

=

Because

of

an

order

from

the

United

States

International

Trade

Commission,

BGA-packaged

product

lines

and

part

numbers

indicated

here

currently

are

not

available

from

Freescale

for

import

or

sale

in

the

United

States

prior

to

September

2010:

i.MX31

Product

Family

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB95F108ANSPMC1 | 16-BIT, FLASH, 16.25 MHz, RISC MICROCONTROLLER, PQFP64 |

| MB89PV530-201CF | MICROCONTROLLER, CQFP64 |

| MC9S08AC96CFGE | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| MPC8572CVTATLB | 32-BIT, 1200 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572ECPXAVLB | 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA1023 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX31WPDK | 功能描述:開發(fā)板和工具包 - ARM I.MX31 WINCE PDK RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| MCIMX32LVK5 | 制造商:Freescale Semiconductor 功能描述:MX32 14X14 - Bulk |

| MCIMX32VK5 | 制造商:Freescale Semiconductor 功能描述:MX32 14X14 - Tape and Reel |

| MCIMX32VK5R2 | 制造商:Freescale Semiconductor 功能描述:MX32 14X14 - Tape and Reel |

| MCIMX35 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Multimedia Applications Processor for Automotive Products |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。