- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9976 > ISLA224S20IR1Z (Intersil)IC ADC PDF資料下載

參數(shù)資料

| 型號(hào): | ISLA224S20IR1Z |

| 廠商: | Intersil |

| 文件頁(yè)數(shù): | 38/38頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ADC |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)

ISLA224S

9

FN7911.2

April 25, 2013

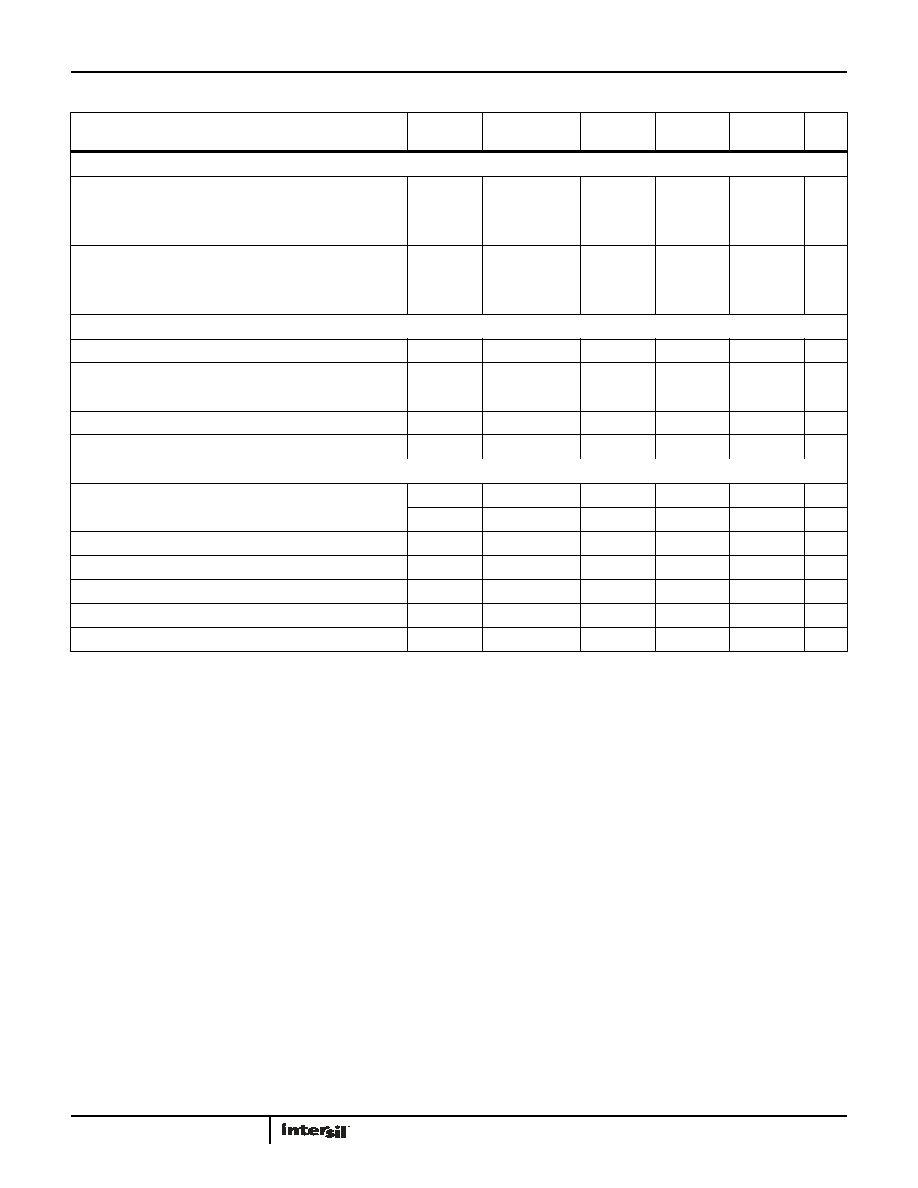

LVDS Inputs

SYNCP, SYNCN Setup Time (with Respect to the Positive Edge of

CLKP)

tRSTS

AVDD,

OVDD = 1.7V to

1.9V, TA = -40°C

to +85°C

400

75

ps

SYNCP, SYNCN Hold Time (with respect to the positive edge of

CLKP)

tRSTH

AVDD,

OVDD = 1.7V to

1.9V, TA = -40°C

to +85°C

150

350

ps

CML Outputs

Output Rise Time

tR

165

ps

Output Fall Time

tF

145

ps

Data Output Duty Cycle

50

%

Differential Output Resistance

100

Differential Output Voltage (Note 13)

760

mVP-P

SCLK Period

t

CLK

Write Operation

7

cycles

tCLK

Read Operation

16

cycles

CSB

↓ to SCLK↑ Setup Time

tS

Read or Write

2

cycles

CSB

↑ after SCLK↑ Hold Time

tH

Read or Write

5

cycles

Data Valid to SCLK

↑ Setup Time

tDS

Read or Write

6

cycles

Data Valid after SCLK

↑ Hold Time

tDH

Read or Write

4

cycles

Data Valid after SCLK

↓ Time

tDVR

Read

4

cycles

NOTES:

11. The Tri-Level Inputs internal switching thresholds are approximately. 0.43V and 1.34V. It is advised to float the inputs, tie to ground or AVDD depending

on desired function.

12. The synchronous clock divider reset function is available as a (SPI-programmable) overload on the SYNC input.

13. The voltage is expressed in peak-to-peak differential swing. The peak-to-peak single-ended swing is 1/2 of the differential swing.

14. The SPI interface timing is directly proportional to the ADC sample period (tS). Values above reflect multiples of a 4ns sample period, and must be

scaled proportionally for lower sample rates. ADC sample clock must be running for SPI communication.

15. The SPI may operate asynchronously with respect to the ADC sample clock.

Switching Specifications Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)

PARAMETER

SYMBOL

CONDITION

MIN

(Note 6)

TYP

MAX

(Note 6)

UNITS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-21L-MX-F1 | CONVERTER MOD DC/DC 28V 75W |

| HI1-674AKD-5 | IC ADC 12BIT 67KSPS 1CH 28-SBDIP |

| VE-J13-MW-B1 | CONVERTER MOD DC/DC 24V 100W |

| MS27656E11A5S | CONN RCPT 5POS WALL MNT W/SCKT |

| IDT72V3641L15PFG | IC SYNCFIFO 1024X36 15NS 120TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISLA224S25 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Dual 14-Bit, 250/200/125 MSPS JESD204B High Speed Serial Output ADC |

| ISLA224S25IR1Z | 功能描述:IC ADC RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:250 系列:- 位數(shù):12 采樣率(每秒):1.8M 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):1.82W 電壓電源:模擬和數(shù)字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-LQFP 供應(yīng)商設(shè)備封裝:48-LQFP(7x7) 包裝:管件 輸入數(shù)目和類型:2 個(gè)單端,單極 |

| ISLA224S25IR48EV1Z | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Dual 12-Bit, 250/200/125 MSPS JESD204B High Speed Serial Output ADC |

| ISLEM-BDGSTKEV1Z | 制造商:Intersil Corporation 功能描述:DAQ ON A STICK, E-MICRO STRAIN GAUGE, EVAL BOARD 1, ROHS COM - Bulk 制造商:Intersil Corporation 功能描述:EVAL BOARD FOR STRAIN GAUGE |

| ISLI2C-KIT | 制造商:Intersil Corporation 功能描述:ISLI2C - USB INTERFACE - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。