- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82K96A (Holtek Semiconductor Inc.) USB Multimedia Keyboard Encoder 8-Bit Mask MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT82K96A |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Multimedia Keyboard Encoder 8-Bit Mask MCU |

| 中文描述: | 的USB多媒體鍵盤編碼器8位微控制器面膜 |

| 文件頁(yè)數(shù): | 9/46頁(yè) |

| 文件大小: | 298K |

| 代理商: | HT82K96A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

HT82K96A

Rev. 1.50

9

August 25, 2006

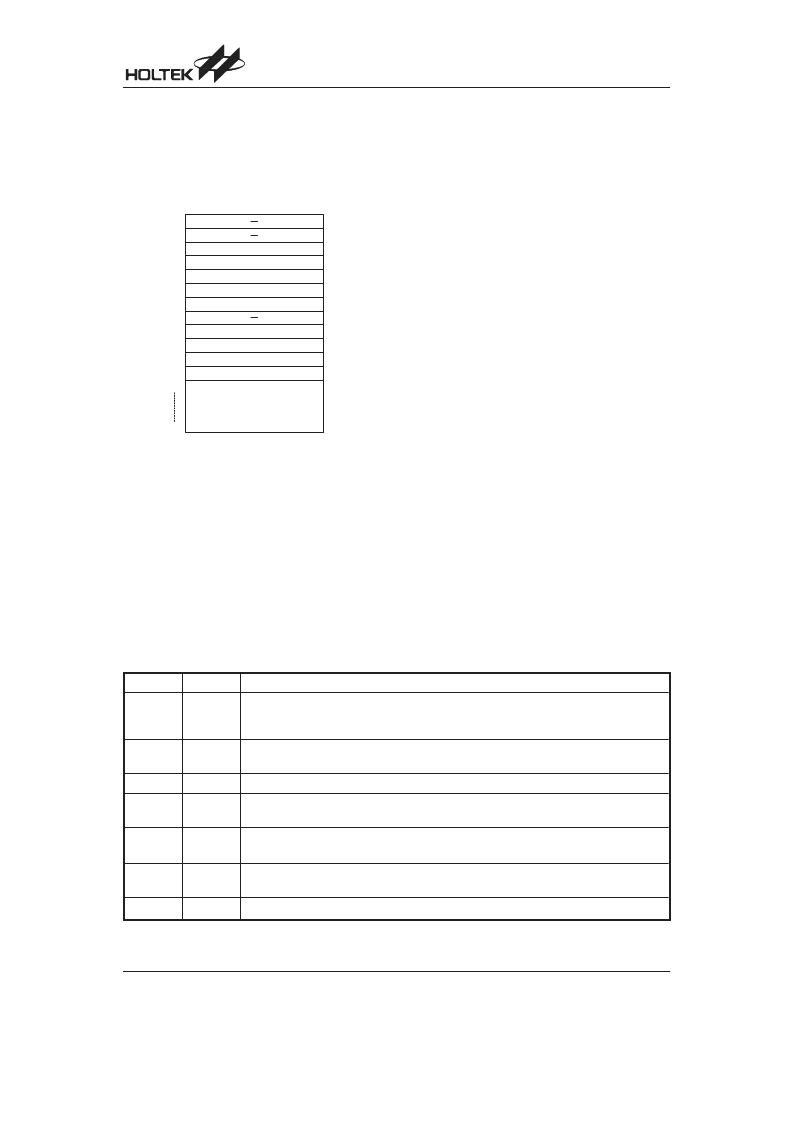

Data Memory

RAM for Bank 1

The special function registers used in USB interface are

located in RAM bank 1. In order to access Bank1 regis-

ter, only the Indirect addressing pointer MP1 can be

usedandtheBankregisterBPshouldsetto1.Themap-

ping of RAM bank 1 is as shown.

Indirect Addressing Register

Location 00H and 02H are indirect addressing registers

that are not physically implemented. Any read/write op-

eration of [00H] ([02H]) will access data memory pointed

to by MP0 (MP1). Reading location 00H (02H) itself indi-

rectly will return the result 00H. Writing indirectly results

in no operation.

The indirect addressing pointer (MP0) always point to

Bank0 RAM addresses no matter the value of Bank

Register (BP).

The indirect addressing pointer (MP1) can access

Bank0 or Bank1 RAM data according the value of BP is

set to 0 or 1 respectively.

The memory pointer registers (MP0 and MP1) are 8-bit

registers.

Accumulator

The accumulator is closely related to ALU operations. It

is also mapped to location 05H of the data memory and

can carry out immediate data operations. The data

movement between two data memory locations must

pass through the accumulator.

Arithmetic and Logic Unit

ALU

This circuit performs 8-bit arithmetic and logic opera-

tions. The ALU provides the following functions:

Arithmetic operations (ADD, ADC, SUB, SBC, DAA)

Logic operations (AND, OR, XOR, CPL)

Rotation (RL, RR, RLC, RRC)

Increment and Decrement (INC, DEC)

Branch decision (SZ, SNZ, SIZ, SDZ ....)

The ALU not only saves the results of a data operation

but also changes the status register.

Status Register

STATUS

This 8-bit register (0AH) contains the zero flag (Z), carry

flag (C), auxiliary carry flag (AC), overflow flag (OV),

power down flag (PDF), and watchdog time-out flag

(TO). It also records the status information and controls

the operation sequence.

With the exception of the TO and PDF flags, bits in

the status register can be altered by instructions like

most other registers. Any data written into the status

register will not change the TO or PDF flag. In addi-

tion operations related to the status register may give

different results from those intended.

Bit No.

Label

Function

0

C

C is set if the operation results in a carry during an addition operation or if a borrow does not

take place during a subtraction operation; otherwise C is cleared. C is also affected by a ro-

tate through carry instruction.

1

AC

ACissetiftheoperationresultsinacarryoutofthelownibblesinadditionornoborrowfrom

the high nibble into the low nibble in subtraction; otherwise AC is cleared.

2

Z

Z is set if the result of an arithmetic or logic operation is zero; otherwise Z is cleared.

3

OV

OV is set if the operation results in a carry into the highest-order bit but not a carry out of the

highest-order bit, or vice versa; otherwise OV is cleared.

4

PDF

PDF is cleared by system power-up or executing the CLR WDT instruction. PDF is set by

executing the HALT instruction.

5

TO

TO is cleared by system power-up or executing the CLR WDT or HALT instruction. TO

is set by a WDT time-out.

6~7

Unused bit, read as 0

Status (0AH) Register

"

%

" D (

!

3

"

%

( %

( =

!

+

# #

: :

: :

: :

: :

7

*

2

*

2

*

2

* 7 2

* * 2

* 0 2

* 1 2

* . 2

* 8 2

* 9 2

*

2

* / 2

*

2

: : 2

RAM Bank 1

Note:

Register 45H is defined for version C or later

version

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82K96E | 8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82M21A | 3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22 | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22A | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M23C | 3/5-Key USB+PS/2 Optical Mouse Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82K96E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82K96E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit OTP MCU |

| HT82M13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mouse/Trackball Controller |

| HT82M21A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M21A_05 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。