- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385404 > HT82K96A (Holtek Semiconductor Inc.) USB Multimedia Keyboard Encoder 8-Bit Mask MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT82K96A |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Multimedia Keyboard Encoder 8-Bit Mask MCU |

| 中文描述: | 的USB多媒體鍵盤編碼器8位微控制器面膜 |

| 文件頁(yè)數(shù): | 23/46頁(yè) |

| 文件大?。?/td> | 298K |

| 代理商: | HT82K96A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

HT82K96A

Rev. 1.50

23

August 25, 2006

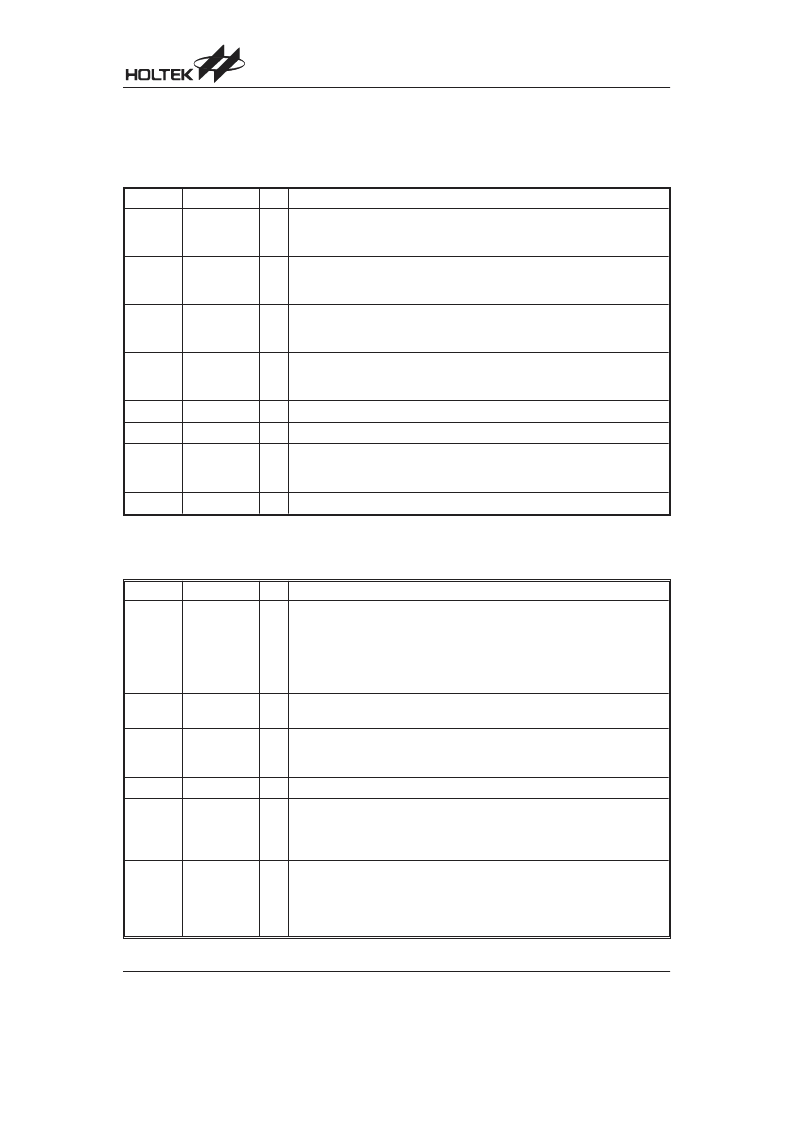

The USR (USB endpoint interrupt status register) register is used to indicate which endpoint is accessed and to select

serial bus (PS2 or USB) and A/D converter operation modes. The endpoint request flags (EP0IF, EP1IF, EP2IF and

EP3IF) are used to indicate which endpoints are accessed. If an endpoint is accessed, the related endpoint request

flag will be set to 1 and the USB interrupt will occur (if USB interrupt is enabled and the stack is not full). When the ac-

tive endpoint request flag is served, the endpoint request flag has to be cleared to 0 .

Bit No.

Label

R/W

Function

0

EP0IF

R/W

When this bit is set to 1 (set by SIE), it indicates the endpoint 0 is accessed and

a USB interrupt will occur. When the interrupt has been served, this bit should be

cleared by firmware.

1

EP1IF

R/W

When this bit is set to 1 (set by SIE), it indicates the endpoint 1 is accessed and

a USB interrupt will occur. When the interrupt has been served, this bit should be

cleared by firmware.

2

EP2IF

R/W

When this bit is set to 1 (set by SIE), it indicates the endpoint 2 is accessed and

a USB interrupt will occur. When the interrupt has been served, this bit should be

cleared by firmware.

3

EP3IF

R/W

When this bit is set to 1 (set by SIE), it indicates the endpoint 3 is accessed and

a USB interrupt will occur. When the interrupt has been served, this bit should be

cleared by firmware.

4

SPS2

R/W The PS2 function is selected when this bit is set to 1 . (Default= 0 )

5

SUSB

R/W The USB function is selected when this bit is set to 1 . (Default= 0 )

6

ADREF

R/W

The reference voltage of A/D converter is coming from the VDD and VSS of MCU

when this bit is set 1 . Otherwise, the reference voltage of A/D converter comes

from external PB6/VRL and PB7/VRH pins. (Default= 1 )

7

FIFO-cntl

W

For ICE only, 0 for FIFO read (Default= 0 ); 1 for FIFO write

USR (1BH) Register

There is a system clock control register implemented to select the clock used in the MCU. This register consists of USB

clock control bit (USBCKEN), second suspend mode control bit (SUSP2) and system clock selection (SYSCLK).

Bit No.

Label

R/W

Function

2~0

Led_on Period R/W

To define low pulse period of IRPT (PC0) for mouse hardware function.

The time base is 31.25 s (1/32kHz). Default value is 000.

000: 2 base

001: 3 base

010: 5 base

011: 9 base

100: 17 base

101: 33 base

110: 65 base

111: 127 base

3

USBCKEN

R/W

USB clock control bit. When this bit is set to 1 , it indicates that the USB clock is

enabled. Otherwise, the USB clock is turned-off. (Default= 0 )

4

SUSP2

R/W

This bit is used for decreasing power consumption in suspend mode.

In normal mode clean this bit=0 (Default= 0 )

In HALT mode set this bit=1 for decreasing power consumption.

5

R/W Undefined, should be cleared to 0

6

SYSCLK

R/W

This bit is used to specify the system oscillator frequency used by MCU. If a

6MHz crystal oscillator or resonator is used, this bit should be set to 1 . If a

12MHz crystal oscillator or resonator is used, this bit should be cleared to 0 (de-

fault).

7

HWKUPSB

R/W

Hardware HALT mode wake-up detect circuit active under power down mode.

Low active.

0 : WDT timer overflow will wake-up MCU system

1 : WDT timer overflow will start hardware wake-up detect circuit but not

wake-up MCU system.

SCC (1CH) Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82K96E | 8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82M21A | 3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22 | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M22A | 5-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M23C | 3/5-Key USB+PS/2 Optical Mouse Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82K96E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit USB Multimedia Keyboard Encoder OTP MCU |

| HT82K96E_07 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Multimedia Keyboard Encoder 8-Bit OTP MCU |

| HT82M13 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mouse/Trackball Controller |

| HT82M21A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

| HT82M21A_05 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:3-Key 3D USB+PS/2 Optical Mouse Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。