- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT48C50- (Holtek Semiconductor Inc.) 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | HT48C50- |

| 廠商: | Holtek Semiconductor Inc. |

| 元件分類: | 數(shù)學(xué)處理器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 7/45頁 |

| 文件大小: | 295K |

| 代理商: | HT48C50- |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

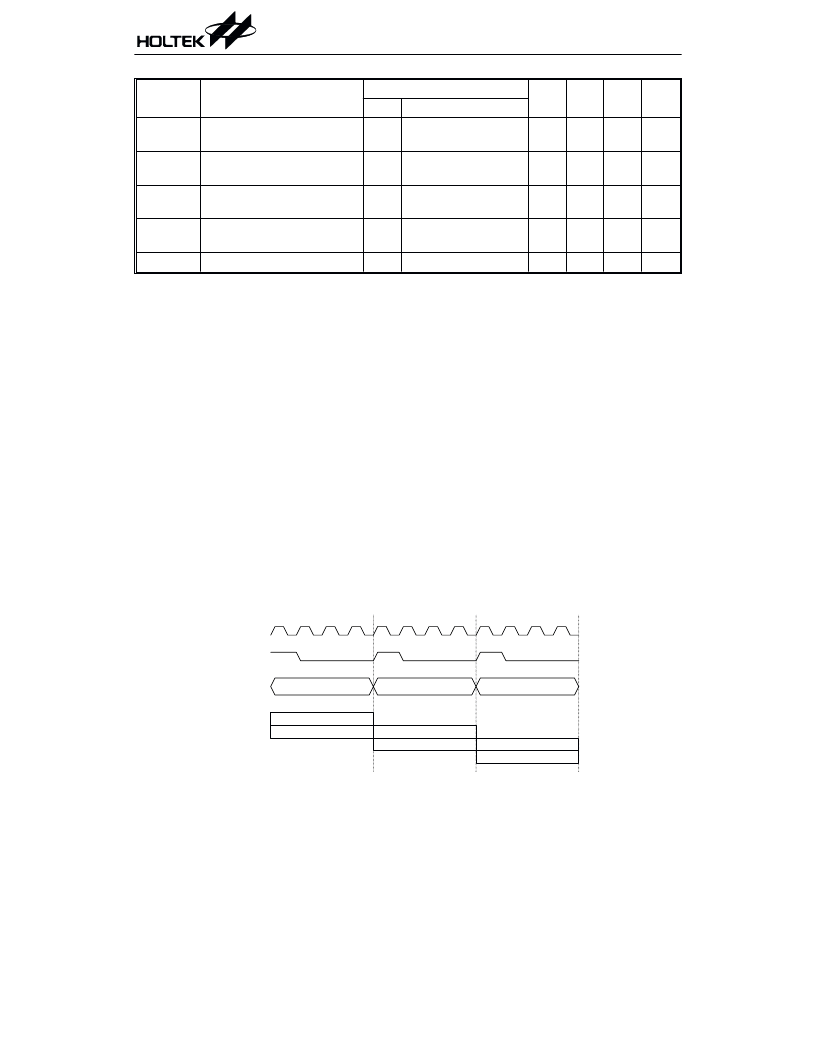

Symbol

Parameter

Test Conditions

Min. Typ. Max. Unit

V

DD

Conditions

t

WDT2

Watchdog Time-out Period

(System Clock)

Without WDT

prescaler

1024

t

SYS

t

WDT3

Watchdog Time-out Period

(RTC OSC)

Without WDT

prescaler

7.812

ms

t

RES

External Reset Low Pulse

Width

1

s

t

SST

System Start-up Timer

Period

Power-up, reset or

wake-up from HALT

1024

t

SYS

t

INT

Interrupt Pulse Width

1

s

Functional Description

HT48C50-1

7

June 14, 2000

Preliminary

Execution flow

The system clock for the microcontroller is de-

rived from either a crystal or an RC oscillator.

The system clock is internally divided into four

non-overlapping clocks. One instruction cycle

consists of four system clock cycles.

Instruction fetching and execution are

pipelined in such a way that a fetch takes an in-

struction cycle while decoding and execution

takes the next instruction cycle. However, the

pipelining scheme causes each instruction to ef-

fectively execute in a cycle. If an instruction

changes the program counter, two cycles are re-

quired to complete the instruction.

Program counter

PC

The program counter (PC) controls the se-

quence in which the instructions stored in the

program ROM are executed and its contents

specify a full range of program memory.

After accessing a program memory word to fetch

an instruction code, the contents of the program

counter are incremented by one. The program

counter then points to the memory word contain-

ing the next instruction code.

When executing a jump instruction, conditional

skip execution, loading PCL register, subrou-

tine call, initial reset, internal interrupt, exter-

nal interrupt or return from subroutine, the PC

manipulates the program transfer by loading

the address corresponding to each instruction.

The conditional skip is activated by instruc-

tions. Once the condition is met, the next in-

struction, fetched during the current

instruction execution, is discarded and a

dummy cycle replaces it to get the proper in-

struction. Otherwise proceed with the next in-

struction.

1

+

1

+

1

+

9 ! ) *

* 6

8

: ! * * 6 ; 8

9 ! ) *

* 6

< 8

: ! * * 6 8

9 ! ) *

* 6

< 8

: ! * * 6 < 8

<

<

& ! * =

* 6 * & 8

Execution flow

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT48C70-1 | I/O Type 8-Bit MCU |

| HT48R70A-1 | I/O Type 8-Bit MCU |

| HT48C70 | 8-Bit Microcontroller Series |

| HT48CA0-2 | Remote Type 8-Bit MCU |

| HT48RA0 | Remote Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT48C50(28SKDIP-H) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| HT48C50(40DIP-A) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| HT48C50-1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit I/O Type Mask MCU |

| HT48C50-1_09 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:I/O Type 8-Bit MCU |

| HT48C70 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit Microcontroller Series |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。