- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R47 (Holtek Semiconductor Inc.) 8-Bit OTP Battery Charger Controller PDF資料下載

參數(shù)資料

| 型號(hào): | HT46R47 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit OTP Battery Charger Controller |

| 中文描述: | 8位檢察官電池充電器控制器 |

| 文件頁(yè)數(shù): | 18/45頁(yè) |

| 文件大小: | 588K |

| 代理商: | HT46R47 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

HT46R47

Rev. 1.40

18

July 18, 2001

on pull-high options). Each bit of these in-

put/outputlatchescanbesetorclearedby SET

[m].i and CLR [m].i (m=12H, 14H or 18H) in-

structions.

Some instructions first input data and then fol-

low the output operations. For example, SET

[m].i , CLR [m].i , CPL [m] , CPLA [m] read

the entire port states into the CPU, execute the

defined operations (bit-operation), and then

write the results back to the latches or the accu-

mulator.

Each line of port A has the capability of wak-

ing-up the device. The highest 4-bit of port B and

7 bits of port D are not physically implemented;

on reading them a 0 is returned whereas writ-

ing then results in a no-operation. See Applica-

tion note.

Each I/O line has a pull-high option. Once the

pull-high option is selected, the I/O line has a

pull-high resistor, otherwise, there s none.

Take note that a non-pull-high I/O line operat-

ing in input mode will cause a floating state.

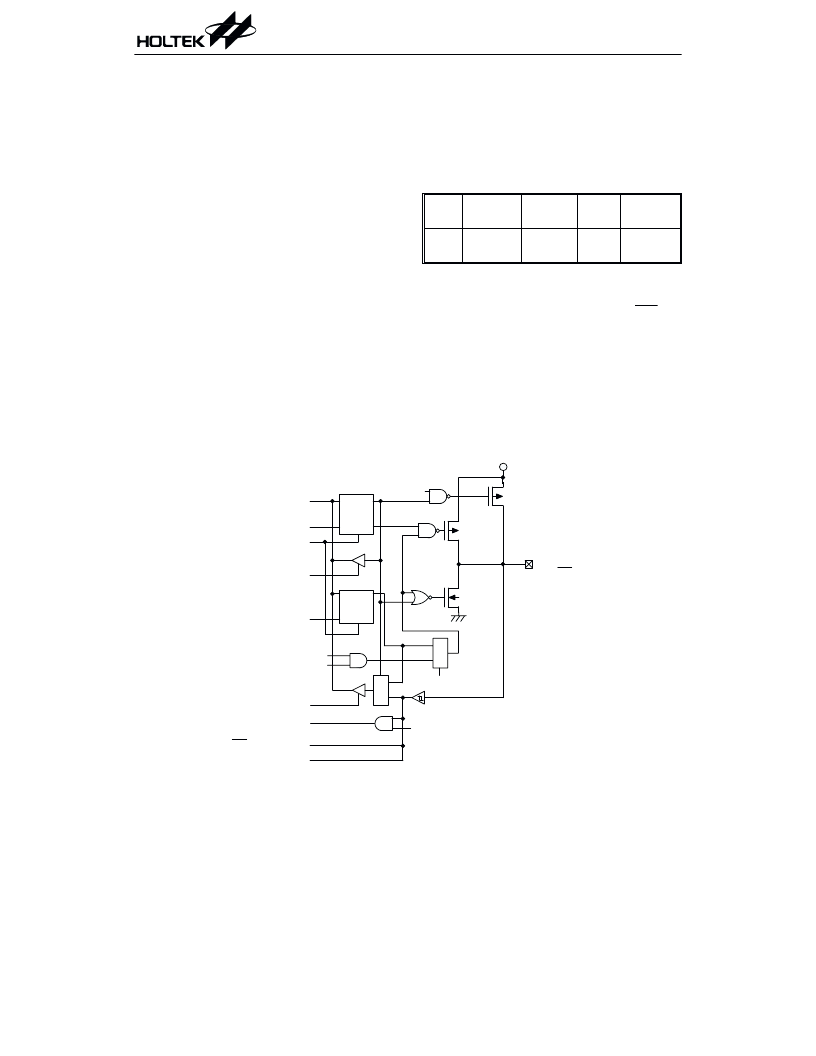

The PA3 is pin-shared with the PFD signal. If

the PFD option is selected, the output signal in

output mode of PA3 will be the PFD signal gen-

erated by timer/event counter overflow signal.

The input mode always remaining its original

functions. Once the PFD option is selected, the

PFD output signal is controlled by PA3 data

register only. Writing 1 to PA3 data register

will enable the PFD output function and writ-

ing 0 will force the PA3 to remain at 0 . The

I/O functions of PA3 are shown below.

I/O

Mode

I/P

(Normal)

O/P

(Normal)

I/P

(PFD)

O/P

(PFD)

PA3

Logical

Input

Logical

Output

Logical

Input

PFD

(Timer on)

Note:

The PFD frequency is the timer/event

counteroverflowfrequencydividedby2.

The PA5 and PA4 are pin-shared with INT and

TMR pins respectively.

The PB can also be used as A/D converter in-

puts. The A/D function will be described later.

There is a PWM function shared with PD0. If

the PWM function is enabled, the PWM signal

will appear on PD0 (if PD0 is operating in out-

put mode). The I/O functions of PD0 are as

shown.

9

:

5

( ) " ' 1

( ) "

- ' 1

1 $ . # +

& = # 7 , /

9 ) - ' 1 :

# & 2 & . & # * 0 $ . # "

9

) "

:

D

!

D

D

!

D

) - . " ) '0 .

& . &, $

" 0 . # ) - . " ) '# * 0 $ . # "

3 0 / # $ # .

" 0 . # & . & # * 0 $ . # "

& . &0 .

5

6

5

Input/output ports

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R65-100 | A/D with LCD Type 8-Bit MCU |

| HT46C65 | A/D with LCD Type 8-Bit MCU |

| HT46C65-100 | A/D with LCD Type 8-Bit MCU |

| HT46C65-52 | A/D with LCD Type 8-Bit MCU |

| HT46C65-56 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R47(18DIP-A) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| HT46R47(18SOP-A) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| HT46R47E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit MCU |

| HT46R47-H | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit OTP MCU |

| HT46R48 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Cost-Effective A/D Type 8-Bit OTP MCU |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。