- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R24 (Holtek Semiconductor Inc.) A/D Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號: | HT46R24 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D Type 8-Bit MCU |

| 中文描述: | 的A / D型8位微控制器 |

| 文件頁數(shù): | 16/49頁 |

| 文件大?。?/td> | 393K |

| 代理商: | HT46R24 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

HT46R24/HT46C24

Rev. 1.50

16

May 3, 2004

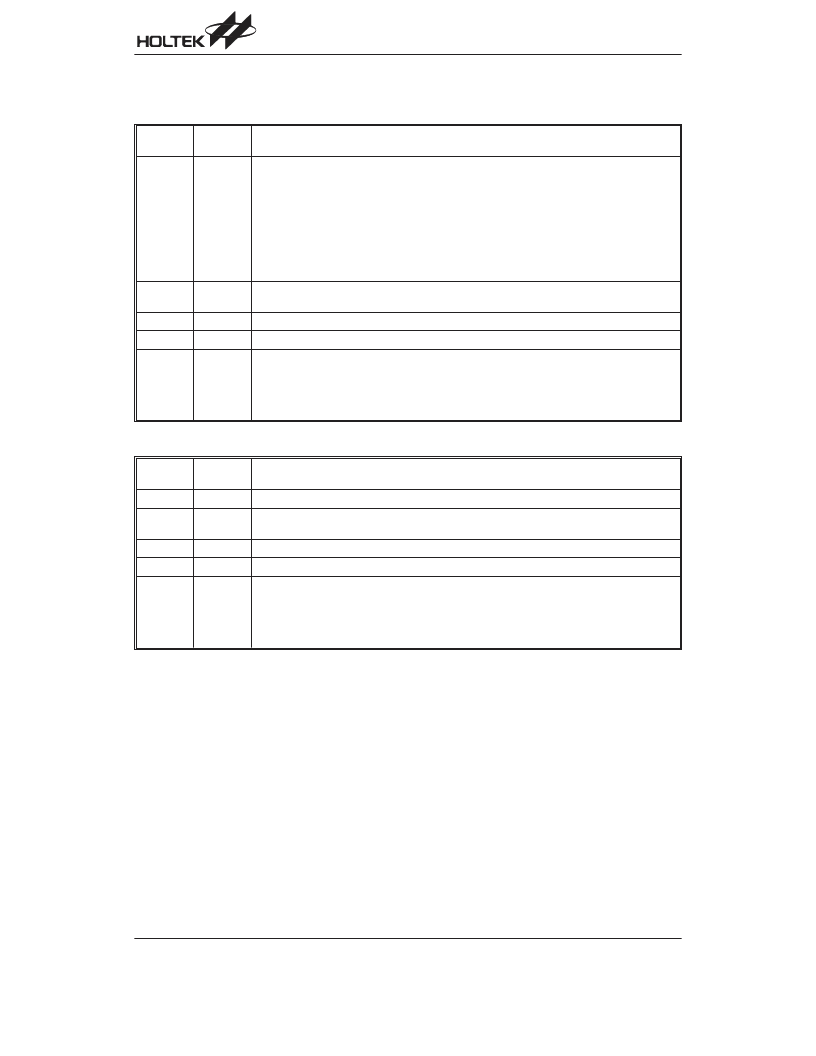

The bit0~bit2 of the TMR0C can be used to define the pre-scaling stages of the internal clock sources of timer/event

counter. The definitions are as shown. The overflow signal of timer/event counter can be used to generate the PFD sig-

nal. The timer prescaler is also used as the PWM counter.

Label

(TMR0C)

Bits

Function

T0PSC0

T0PSC1

T0PSC2

0

1

2

Defines the prescaler stages, T0PSC2, T0PSC1, T0PSC0=

000: f

INT

=f

SYS

001: f

INT

=f

SYS

/2

010: f

INT

=f

SYS

/4

011: f

INT

=f

SYS

/8

100: f

INT

=f

SYS

/16

101: f

INT

=f

SYS

/32

110: f

INT

=f

SYS

/64

111: f

INT

=f

SYS

/128

T0E

3

Defines the TMR active edge of timer/ event counter

(0=active on low to high; 1=active on high to low)

T0ON

4

Enable/disable timer counting (0=disabled; 1=enabled)

5

Unused bit, read as 0

T0M0

T0M1

6

7

Defines the operating mode, T0M1, T0M0:

01=Event count mode (external clock)

10=Timer mode (internal clock)

11=Pulse width measurement mode

00=Unused

TMR0C Register

Label

(TMR1C)

Bits

Function

0~2

Unused bit, read as 0

T1E

3

Defines the TMR active edge of timer/ event counter

(0=active on low to high; 1=active on high to low)

T1ON

4

Enable/disable timer counting (0=disabled; 1=enabled)

5

Unused bit, read as 0

T1M0

T1M1

6

7

Defines the operating mode, T1M1, T1M0:

01=Event count mode (external clock)

10=Timer mode (internal clock)

11=Pulse width measurement mode

00=Unused

TMR1C Register

Input/Output Ports

There are 40 bidirectional input/output lines in the

microcontroller, labeled as PA, PB, PC, PD and PF,

which are mapped to the data memory of [12H], [14H],

[16H],[18H]and[28H]respectively.AlloftheseI/Oports

can be used for input and output operations. For input

operation, these ports are non-latching, that is, the in-

puts must be ready at the T2 rising edge of instruction

MOV A,[m] (m=12H, 14H, 16H, [18H] or 28H). For out-

put operation, all the data is latched and remains un-

changed until the output latch is rewritten.

Each I/O line has its own control register (PAC, PBC,

PCC, PDC, PFC) to control the input/output configura-

tion. With this control register, CMOS output or Schmitt

trigger input with or without pull-high resistor structures

canbereconfigureddynamicallyundersoftwarecontrol.

To function as an input, the corresponding latch of the

control register must write 1 . The input source also de-

pends on the control register. If the control register bit is

1 , the input will read the pad state. If the control regis-

ter bit is 0 , the contents of the latches will move to the

internal bus. The latter is possible in the read-modify-

write instruction.

For output function, CMOS is the only configuration.

These control registers are mapped to locations 13H,

15H, 17H, 19H and 29H.

Afterachipreset,theseinput/outputlinesremainathigh

levels or floating state (depends on pull-high options).

Each bit of these input/output latches can be set or

cleared by SET [m].i and CLR [m].i (m=12H, 14H,

16H 18H or 28H) instructions.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46C46 | Cost-Effective A/D Type 8-Bit MCU |

| HT46C47 | Cost-Effective A/D Type 8-Bit MCU |

| HT46R46 | Cost-Effective A/D Type 8-Bit MCU |

| HT46C62 | A/D with LCD Type 8-Bit MCU |

| HT46R62 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R24_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU |

| HT46R32 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit OTP MCU with OPA |

| HT46R321 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit OTP MCU with OPA and 8x4 LED Driver |

| HT46R322 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with OPA Type 8-Bit OTP MCU |

| HT46R34 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit OTP MCU with OPA |

發(fā)布緊急采購,3分鐘左右您將得到回復。