- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46C64 (Holtek Semiconductor Inc.) A/D with LCD Type 8-Bit MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT46C64 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | A/D with LCD Type 8-Bit MCU |

| 中文描述: | 在A / D液晶型8位微控制器 |

| 文件頁數(shù): | 15/47頁 |

| 文件大?。?/td> | 345K |

| 代理商: | HT46C64 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

HT46R64/HT46C64

Rev. 1.40

15

September 21, 2004

When an interrupt request flag is set before entering the

HALT status, the system cannot be awakened using

that interrupt.

If wake-up events occur, it takes 1024 t

SYS

(system

clock period) to resume normal operation. In other

words, a dummy period is inserted after the wake-up. If

the wake-up results from an interrupt acknowledgment,

the actual interrupt subroutine execution is delayed by

more than one cycle. However, if the wake-up results in

the next instruction execution, the execution will be per-

formed immediately after the dummy period is finished.

To minimize power consumption, all the I/O pins should

be carefully managed before entering the HALT status.

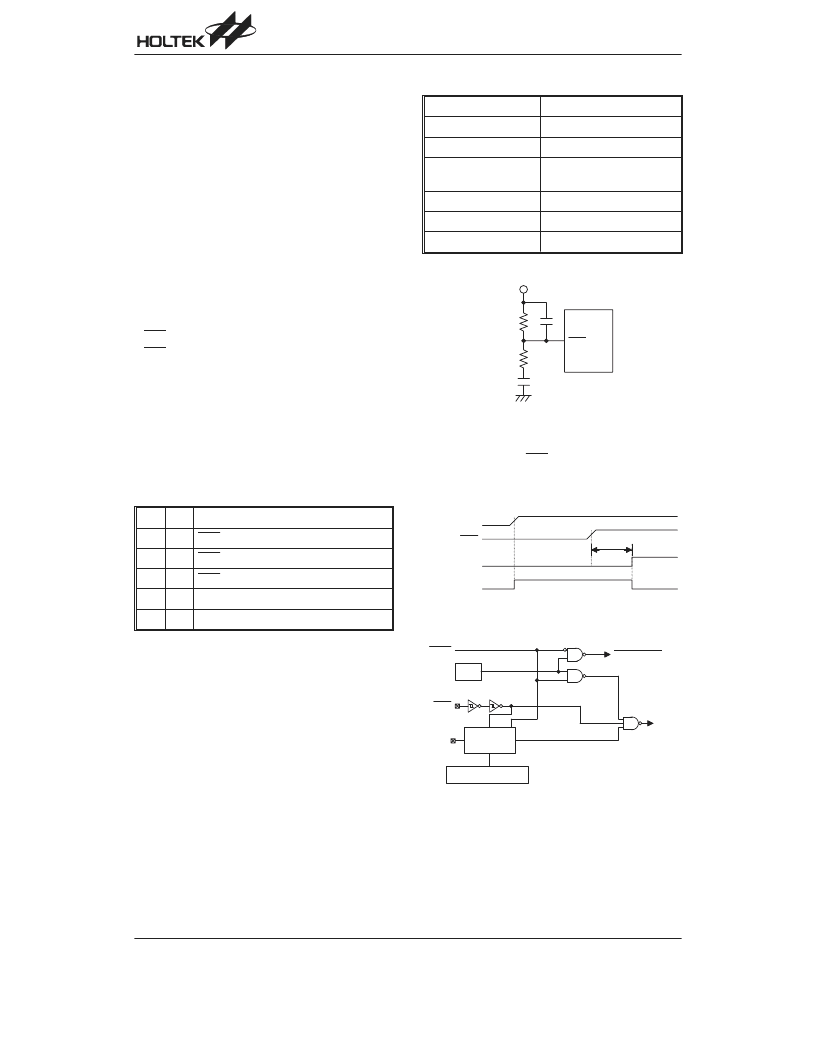

Reset

There are three ways in which reset may occur.

RES is reset during normal operation

RES is reset during HALT

WDT time-out is reset during normal operation

The WDT time-out during HALT differs from other chip

reset conditions, for it can perform a warm reset that

resets only the PC and SP and leaves the other circuits

at their original state. Some registers remain unaffected

during any other reset conditions. Most registers are re-

set to the initial condition once the reset conditions are

met. Examining the PDF and TO flags, the program can

distinguish between different chip resets .

TO

PDF

RESET Conditions

0

0

RES reset during power-up

u

u

RES reset during normal operation

0

1

RES Wake-up HALT

1

u

WDT time-out during normal operation

1

1

WDT Wake-up HALT

Note: u stands for unchanged

To guarantee that the system oscillator is started and

stabilized, the SST (System Start-up Timer) provides an

extra-delay of 1024 system clock pulses when the sys-

tem awakes from the HALT state or during power up.

Awaking from the HALT state or system power-up, the

SST delay is added.

An extra SST delay is added during the power-up pe-

riod, and any wake-up from HALT may enable only the

SST delay.

The functional unit chip reset status is shown below.

PC

000H

Interrupt

Disabled

Prescaler, Divider

Cleared

WDT,RTC,TimeBase

Cleared. After master reset,

WDT starts counting

Timer/event Counter

Off

Input/output Ports

Input mode

SP

Pointstothetopofthestack

+ +

+

+ D

3 E

+ D +

3 E

Reset Circuit

Note:

* Make the length of the wiring, which is con-

nected to the RES pin as short as possible, to

avoid noise interference.

(

5

%

( (

Reset Timing Chart

'

8 " $

'

5

=

6

6

A

5

(

+ 5 @

(

6

'

(

Reset Configuration

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46R64 | A/D with LCD Type 8-Bit MCU |

| HT46R23 | 8-Bit OTP Microcontroller |

| HT46R47 | 8-Bit OTP Battery Charger Controller |

| HT46R65-100 | A/D with LCD Type 8-Bit MCU |

| HT46C65 | A/D with LCD Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46C64_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C65 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C65_11 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C65-100 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

| HT46C65-52 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D with LCD Type 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。