- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385396 > HSP50215 (Intersil Corporation) Digital UpConverter(數(shù)字上變頻器) PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50215 |

| 廠商: | Intersil Corporation |

| 英文描述: | Digital UpConverter(數(shù)字上變頻器) |

| 中文描述: | 數(shù)字上變頻器(數(shù)字上變頻器) |

| 文件頁數(shù): | 13/21頁 |

| 文件大?。?/td> | 162K |

| 代理商: | HSP50215 |

3-13

The convolution multiplies C0 by the most recent data

sample. For a 16 tap, interpolate-by-4 filter, the calculations

are:

OUTPUT0 = (C0*D[n]) + (C4*D[n-1]) + (C8*D[n-2]) +

(C12*D[n-3])

OUTPUT1 = (C1*D[n]) + (C5*D[n-1]) + (C9*D[n-2]) +

(C13*D[n-3])

OUTPUT2 = (C2*D[n]) + (C6*D[n-1]) + (C10*D[n-2]) +

(C14*D[n-3])

OUTPUT3 = (C3*D[n]) + (C7*D[n-1]) + (C11*D[n-2]) +

(C15*D[n-3])

Table 6 indicates how the I coefficients should be loaded for

this example. Notice that 16 filter coefficients are required.

All other addresses not used. The filter interpolates by 4

and the coefficients are loaded sequentially through the 4

interpolation phases starting at 512 - 515, then jumping to

528 - 531 for the next four addresses, and so on until 16

coefficients have been loaded.

Shaping filter Q coefficients are loaded from the first

coefficient (B0) in address 0x300h to the last address in

0x3FFh. The convolution multiplies B0 by the most recent

data sample. For a 16 tap, interpolate-by-4 filter, the

calculations are:

OUTPUT0 = (B0*D[n]) + (B4*D[n-1]) + (B8*D[n-2]) +

(B12*D[n-3])

OUTPUT1 = (B1*D[n]) + (B5*D[n-1]) + (B9*D[n-2]) +

(B13*D[n-3])

OUTPUT2 = (B2*D[n]) + (B6*D[n-1]) + (B10*D[n-2]) +

(B14*D[n-3])

OUTPUT3 = (B3*D[n]) + (B7*D[n-1]) + (B11*D[n-2]) +

(B15*D[n-3])

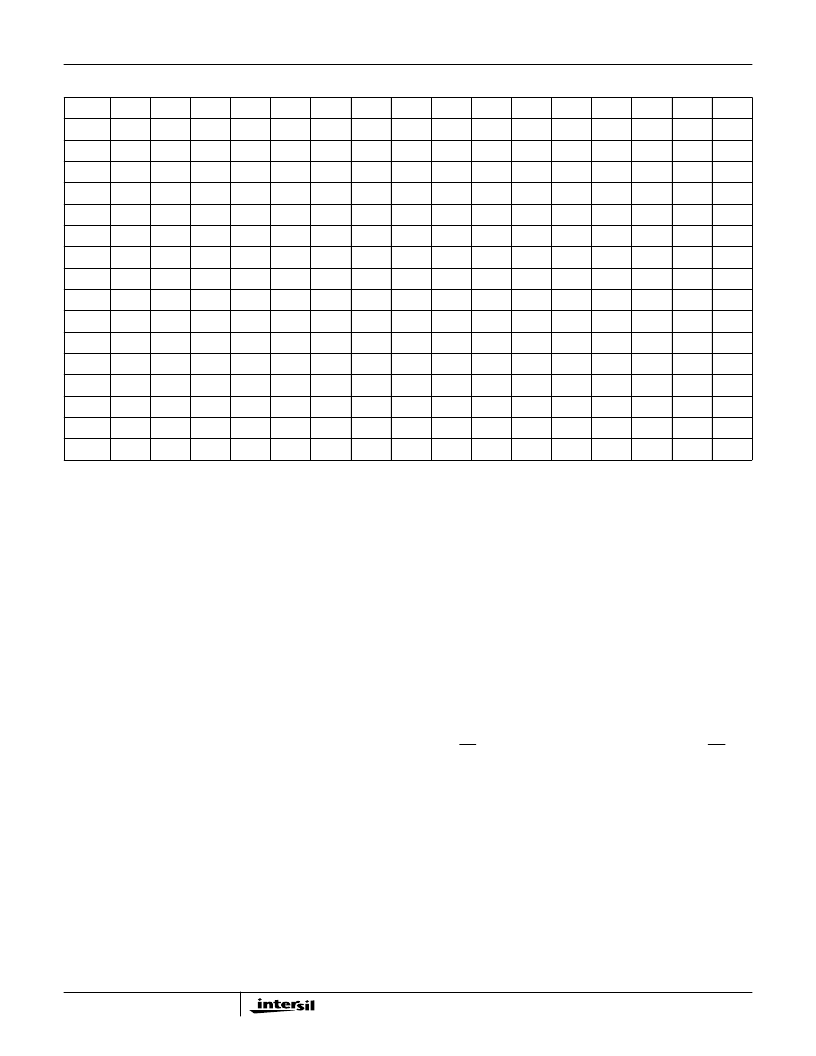

Table 7 indicates how the Q coefficients should be loaded for

this example. Identical to the I filter, notice that since 16 filter

coefficients are required. All other addresses not used. The

filter interpolates by 4, and the coefficients are loaded

sequentially through the 4 interpolation phases, starting at

768-771, then jumping to 784-787 for the next four addresses,

and so on until 16 coefficients have been loaded.

Microprocessor Read

The DUC offers the microprocessor access to all of the

control data configuration registers through a read process.

The shaping filter coefficients, however, cannot be read.

With CE asserted, a “read” consists of dropping the RD line

low to transfer data from the register addresses selected by

A(9:0). The read address mapping is provided in Table 8.

The timing is detailed in Figure 15.

TABLE 6. Q SHAPING FILTER COEFFICIENT ADDRESSES

DS

0

DS

1

DS

2

DS

3

DS

4

DS

5

DS

6

DS

7

DS

8

DS

9

DS

10

DS

11

DS

12

DS

13

DS

14

DS

15

IP0

768

784

800

816

832

848

864

880

896

912

928

944

960

976

992

1008

IP1

769

785

801

817

833

849

865

881

897

913

929

945

961

977

993

1009

IP2

770

786

802

818

834

850

866

882

898

914

930

946

962

978

994

1010

IP3

771

787

803

819

835

851

867

883

899

915

931

947

963

979

995

1011

IP4

772

788

804

820

836

852

868

884

900

916

932

948

964

980

996

1012

IP5

773

789

805

821

837

853

869

885

901

917

933

949

965

981

997

1013

IP6

774

790

806

822

838

854

870

886

902

918

934

950

966

982

998

1014

IP7

775

791

807

823

839

855

871

887

903

919

935

951

967

983

999

1015

IP8

776

792

808

824

840

856

872

888

904

920

936

952

968

984

1000

1016

IP9

777

793

809

825

841

857

873

889

905

921

937

953

969

985

1001

1017

IP10

778

794

810

826

842

858

874

890

906

922

938

954

970

986

1002

1018

IP11

779

795

811

827

843

859

875

891

907

923

939

955

971

987

1003

1019

IP12

780

796

812

828

844

860

876

892

908

924

940

956

972

988

1004

1020

IP13

781

797

813

829

845

861

877

893

909

925

941

957

973

989

1005

1021

IP14

782

798

814

830

846

862

878

894

910

926

942

958

974

990

1006

1022

IP15

783

799

815

831

847

863

879

895

911

927

943

959

975

991

1007

1023

HSP50215

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50216 | Four-Channel Programmable Digital DownConverter(四通道可編程數(shù)字下變頻器) |

| HSP50307 | Burst QPSK Modulator(混合信號(hào)QPSK調(diào)制器) |

| HSP50415VI | CABLE ASSEMBLY; 75 OHM TNC MALE TO 75 OHM TNC MALE; 75 OHM, RG6A/U COAX |

| HSP50415EVAL1 | HSP50415EVAL1 Evaluation Kit |

| HSP9501 | Programmable Data Buffer(可編程數(shù)據(jù)緩沖器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50215EVAL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:DSP Modulator Evaluation Board |

| HSP50215VC | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

| HSP50215VI | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

| HSP50216 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Four-Channel Programmable Digital Downconverter |

| HSP50216_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Four-Channel Programmable Digital DownConverter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。