- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385376 > HFA3860BIV96 (HARRIS SEMICONDUCTOR) nullDirect Sequence Spread Spectrum Baseband Processor PDF資料下載

參數(shù)資料

| 型號: | HFA3860BIV96 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | nullDirect Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP48 |

| 文件頁數(shù): | 26/40頁 |

| 文件大小: | 272K |

| 代理商: | HFA3860BIV96 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

4-26

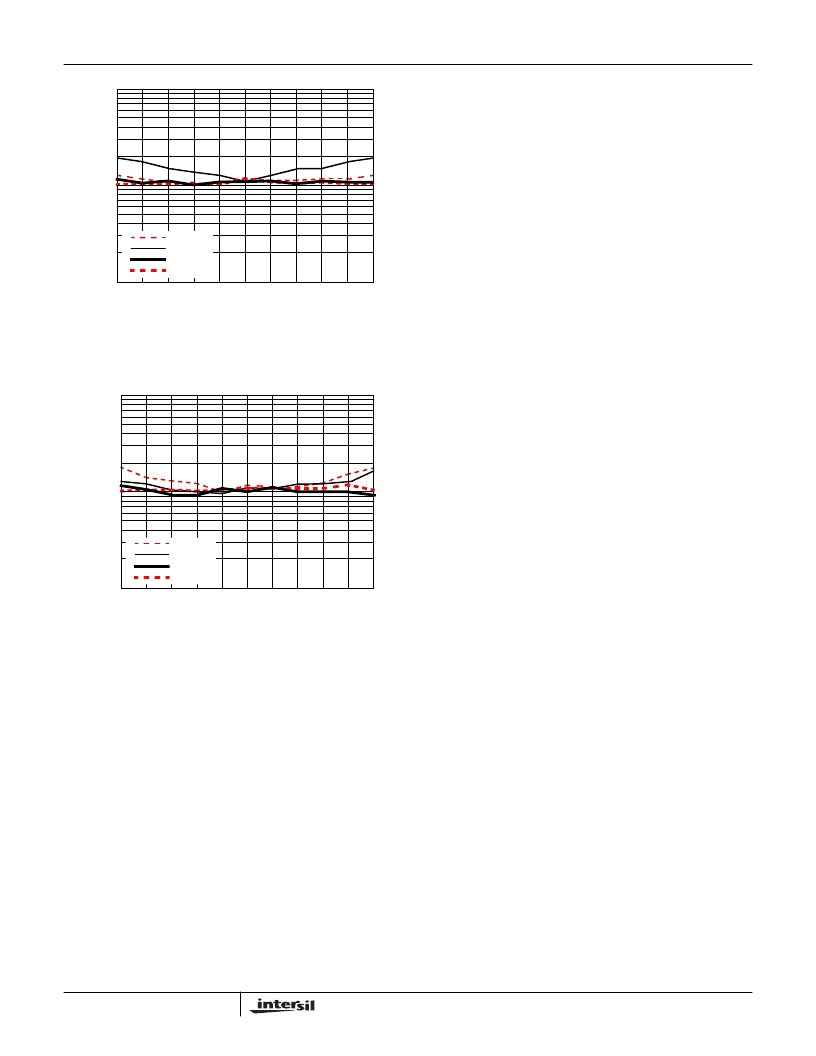

Clock Offset Tracking Performance

The PRISM baseband processor is designed to accept data

clock offsets of up to

±

25ppm for each end of the link (TX

and RX). This effects both the acquisition and the tracking

performance of the demodulator. The budget for clock offset

error is 0.75dB at

±

50ppm and the performance is shown in

Figure 18. This figure shows that the baseband processor in

the high rate modes is better than at low rates in tracking

clock offsets. The data for this figure and the next one was

taken with the SNR into the receiver set to achieve 1E

-5

BER

with no offset. Then the offset was varied to determine the

change in performance.

Carrier Offset Frequency Performance

The correlators used for acquisition for all modes and for

demodulation in the 1 and 2Mbps modes are time invariant

matched filter correlators otherwise known as parallel

correlators. They use two samples per chip and are tapped at

every other shift register stage. Their performance with carrier

frequency offsets is determined by the phase roll rate due to

the offset. For an offset of +50ppm (combined for both TX and

RX) will cause the carrier to phase roll 22.5 degrees over the

length of the correlator. This causes a loss of 0.22dB in

correlation magnitude which translates directly to Eb/N0

performance loss. In the PRISM chip design, the correlator is

not included in the carrier phase locked loop correction, so

this loss occurs for both acquisition and data. In the high rate

modes, the data demodulation is done with a set of correlators

that are included in the carrier tracking loop, so the loss is

less. Figure 19 shows the loss versus carrier offset taken out

to +75ppm (120kHz is 50ppm at 2.4GHz).

FIGURE 18. BER vs CLOCK OFFSET

CLOCK OFFSET (PPM)

-50

-40

-30

-20

-10

0

10

20

30

40

50

BER 1.0

BER 2.0

BER 5.5

BER 11

1.00E

-04

1.00E

-05

1.00E

-06

FIGURE 19. BER vs CARRIER OFFSET

-50

-40

-30

CARRIER OFFSET AT 2.4GHz (PPM)

-20

-10

0

10

20

30

40

50

1.00E

-04

1.00E

-05

1.00E

-06

B

BER 1.0

BER 2.0

BER 5.5

BER 11

HFA3860B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HFA3861BIN | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861BIN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925IA | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA3925IA96 | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA50PA60C | RxxP2xx Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 05V; Output Voltage (Vdc): 15V; Power: 2W; EN 60950 certified, rated for 250VAC; UL-60950-1 / CSA C22.2 certified; 5.2kVDC Isolation for 1 Minute; Optional Continuous Short Circuit Protected; Wide Operating Temperature Range atfull 2 Watts Load, ?40??C to +85??C; Twin Chamber Transformer System; UL94V-0 Package Material; Efficiency to 80% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HFA3860IV | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HFA3860IV WAF | 制造商:Harris Corporation 功能描述: |

| HFA3860IV96 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:11 Mbps Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processo |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。