- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370379 > GS1532* Serializer for HD-SDI. SD-SDI & DVB-ASI. 3.3/1.8V supply. PDF資料下載

參數(shù)資料

| 型號: | GS1532* |

| 英文描述: | Serializer for HD-SDI. SD-SDI & DVB-ASI. 3.3/1.8V supply. |

| 中文描述: | 序列化的HD - SDI信號。標(biāo)清SDI |

| 文件頁數(shù): | 5/39頁 |

| 文件大小: | 631K |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

GENNUM CORPORATION

21498-1

5 of 39

G

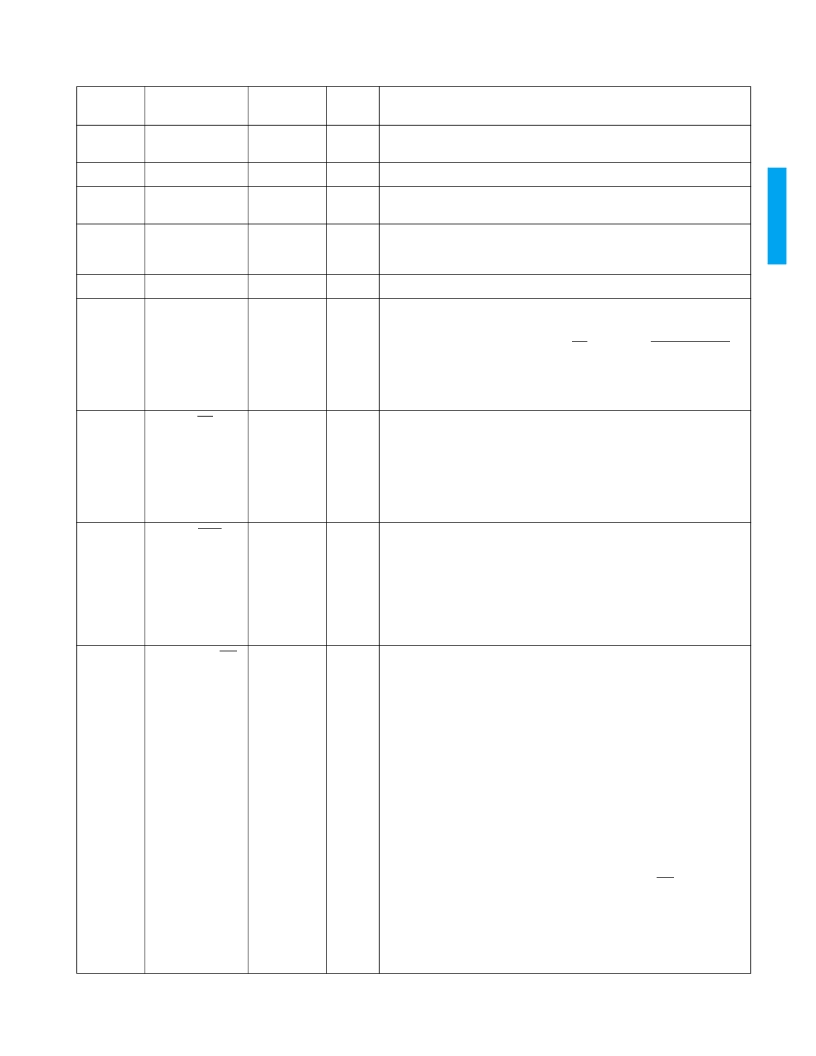

1.2 PIN DESCRIPTIONS

PIN

NUMBER

NAME

TIMING

TYPE

DESCRIPTION

1

CP_VDD

-

Power

Power supply connection for the charge pump. Connect to +3.3V DC

analog.

2

PD_GND

-

Power

Ground connection for the phase detector. Connect to analog GND.

3

PD_VDD

-

Power

Power supply connection for the phase detector. Connect to +1.8V DC

analog.

4, 6 - 8,

10, 14 -17,

31, 70 - 71

NC

-

-

No connect.

5

RSV

-

-

Reserved – connect to analog ground.

9

DVB_ASI

Non

Synchronous

Input

CONTROL SIGNAL INPUT

Signal levels are LVCMOS/LVTTL compatible.

When set HIGH in conjunction with SD/HD = HIGH and SMPTE_BYPASS =

LOW, the device will be configured to operate in DVB-ASI mode.

When set LOW, the device will not support the encoding of received DVB-

ASI data.

11

SD/HD

Non

Synchronous

Input

CONTROL SIGNAL INPUT

Signal levels are LVCMOS/LVTTL compatible.

When set LOW, the device will be configured to transmit signal rates of

1.485Gb/s or 1.485/1.001Gb/s only.

When set HIGH, the device will be configured to transmit signal rates of

270Mb/s only.

12

20bit/10bit

Non

Synchronous

Input

CONTROL SIGNAL INPUT

Signal levels are LVCMOS/LVTTL compatible.

Used to select the input data bus width in SMPTE or Data-Through modes.

This signal is ignored in DVB-ASI mode.

When set HIGH, the parallel input will be 20-bit demultiplexed data.

When set LOW, the parallel input will be 10-bit multiplexed data.

13

IOPROC_EN/DIS

Non

Synchronous

Input

CONTROL SIGNAL INPUT

Signal levels are LVCMOS/LVTTL compatible.

Used to enable or disable I/O processing features.

When set HIGH, the following I/O processing features of the device are

enabled:

EDH Packet Generation and Insertion (SD-only)

SMPTE 352M Packet Generation and Insertion

ANC Data Checksum Calculation and Insertion

Line-based CRC Generation and Insertion (HD-only)

Line Number Generation and Insertion (HD-only)

TRS Generation and Insertion

Illegal Code Remapping

To enable a subset of these features, keep IOPROC_EN/DIS HIGH and

disable the individual feature(s) in the IOPROC_DISABLE register

accesible via the host interface.

When set LOW, the I/O processing features of the device are disabled,

regardless of whether the features are enabled in the IOPROC_DISABLE

register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS1535 | Multi-rate Reclocker for HD-SDI. SD-SDI & DVB-ASI. 3.3V supply. |

| GS1560A* | Reclocking deserializer for HD-SDI. SD-SDI & DVB-ASI with loop thru cable driver. 3.3/1.8V supply. |

| GS1561* | Reclocking deserializer for HD-SDI. SD-SDI & DVB-ASI without loop thru cable driver. 3.3/1.8V supply. |

| GS15T48-5 | 15W DC-DC CONVERTER |

| GS15T48 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS1532_07 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:Multi-Rate Serializer with ClockCleaner |

| GS1532-CF | 制造商:Rochester Electronics LLC 功能描述: 制造商:Gennum Corporation 功能描述: |

| GS1532-CFE3 | 制造商:Gennum Corporation 功能描述:Multi Rate Serializer 80-Pin LQFP |

| GS1535 | 制造商:GENNUM 制造商全稱:GENNUM 功能描述:GS1535 HD-LINX II-TM Multi-Rate SDI Automatic Reclocker |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。