- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375780 > FDW2520C (Analog Devices, Inc.) Thermoelectric Cooler Controller PDF資料下載

參數(shù)資料

| 型號: | FDW2520C |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Thermoelectric Cooler Controller |

| 中文描述: | 熱電冷卻器控制器 |

| 文件頁數(shù): | 16/24頁 |

| 文件大?。?/td> | 416K |

| 代理商: | FDW2520C |

REV. C

–16–

ADN8830

The gate drive outputs for the PWM amplifier at P1 (Pin 21)

and N1 (Pin 22) have a typical nonoverlap delay of 65 ns.

This is done to ensure that one FET is completely off before

the other FET is turned on, preventing current from shooting

through both simultaneously.

The input capacitance (C

ISS

) of the FET should not exceed 5 nF.

The P1 and N1 outputs from the ADN8830 have a typical output

impedance of 6

. This creates a time constant in combination

with C

ISS

of the external FETs equal to 6

C

ISS

. To ensure

shoot-through does not occur through these FETs, this time

constant should remain less than 30 ns.

The linear output from the ADN8830 uses N2 (Pin 10) and

P2 (Pin 11) to drive the gates of the linear side FETs, shown as

Q3 and Q4 in Figure 1. Local compensation for the linear ampli-

fier is achieved through the gate-to-drain capacitances (C

GD

) of

Q3 and Q4. The value of C

GD

, which can be determined from

the data sheet, is usually referred to as C

RSS

, the reverse transfer

capacitance. The exact C

RSS

value should be determined from a

graph that shows capacitance versus drain-to-source voltage,

using the power supply voltage as the appropriate V

DS

.

To ensure stability of the linear amplifier, the total C

GD

of the

PMOS device, Q3, should be greater than 2.5 nF and the total

C

GD

of the NMOS should be greater than 150 pF. External

capacitance can be added around the FET to increase the effective

C

GD

of the transistor. This is the function of C6 in the typical

application schematic shown in Figure 1. If external capacitance

must be added, it will generally only be required around the

PMOS transistor.

In the event of zero output current through the TEC, there will

be no current flowing through Q3 and Q4. In this condition,

these FETs will not provide any small signal gain and thus no

negative feedback for the linear amplifier. This leaves only a

feedforward signal path through C

GD

, which could cause a

settling problem at OUT B. This is often seen as a small signal

oscillation at OUT B, but only when the TEC is at or very near

zero current.

The remedy for this potential minor instability is to add

capacitance from OUT B to ground. This may need to be deter-

mined empirically, but a good starting point is 1.5 times the

total C

GD

. This is the function of C12 in Figure 1. Note that

while adding more C

GD

around Q3 and Q4 will help to ensure

stability, it could potentially increase instability in the zero current

dead band region, requiring additional capacitance from

OUT B to ground.

Bear in mind that the addition of these capacitors is only

for local stabilization. The stability of the entire TEC appli-

cation may need adjustment, which should be done around the

compensation amplifier. This is covered in the Compensation

Loop section.

There is one additional consideration for selecting both the

linear output FETs; they must have a minimum threshold

voltage (V

T

) of 0.6 V. Lower threshold voltages could cause

shoot-through current in the linear output transistors.

Table V shows the recommended FETs that can be used for the

linear output in the ADN8830 application. Table V includes the

appropriate external gate-to-drain capacitance (external C

GD

)

and snubber capacitor value (C

SNUB

) connected from OUT B to

ground that should be added to ensure local stability. Table VI

shows the recommended PWM output FETs. Although other

transistors can be used, these combinations have been tested

and are proved stable and reliable for typical applications.

Data sheets for these devices can be found at their respective

websites:

Fairchild

–

www.fairchildsemi.com

Vishay Siliconix

–

www.vishay.com

International Rectifier

–

www.irf.com

Calculating Power Dissipation and Efficiency

The total efficiency of the ADN8830 application circuit is simply

the ratio of the output power to the TEC divided by the total

power delivered from the supply. The idea in minimizing power

dissipation is to avoid both drawing additional power and reduc-

ing heat generated from the circuit. The dominant sources

of power dissipation will include resistive losses, gate charge

loss, core loss from the inductor, and the current used by the

ADN8830 itself.

The on-channel resistance of both the linear and PWM output

FETs will affect efficiency primarily at high output currents.

Because the linear amplifier operates in a high gain configuration,

it will be at either ground or V

DD

when significant current is

flowing through the TEC. In this condition, the power dissipation

through the linear output FET will be

P

r

I

FET LIN

,

DS ON

,

TEC

=

×

2

(34)

using either the

r

DS, ON

for the NMOS or the PMOS depending

on the direction of the current flow. In the typical application

setup in Figure 2, if the TEC is cooling the target object, the

PMOS is sourcing the current. If the TEC is heating the

object, the NMOS will be sinking current.

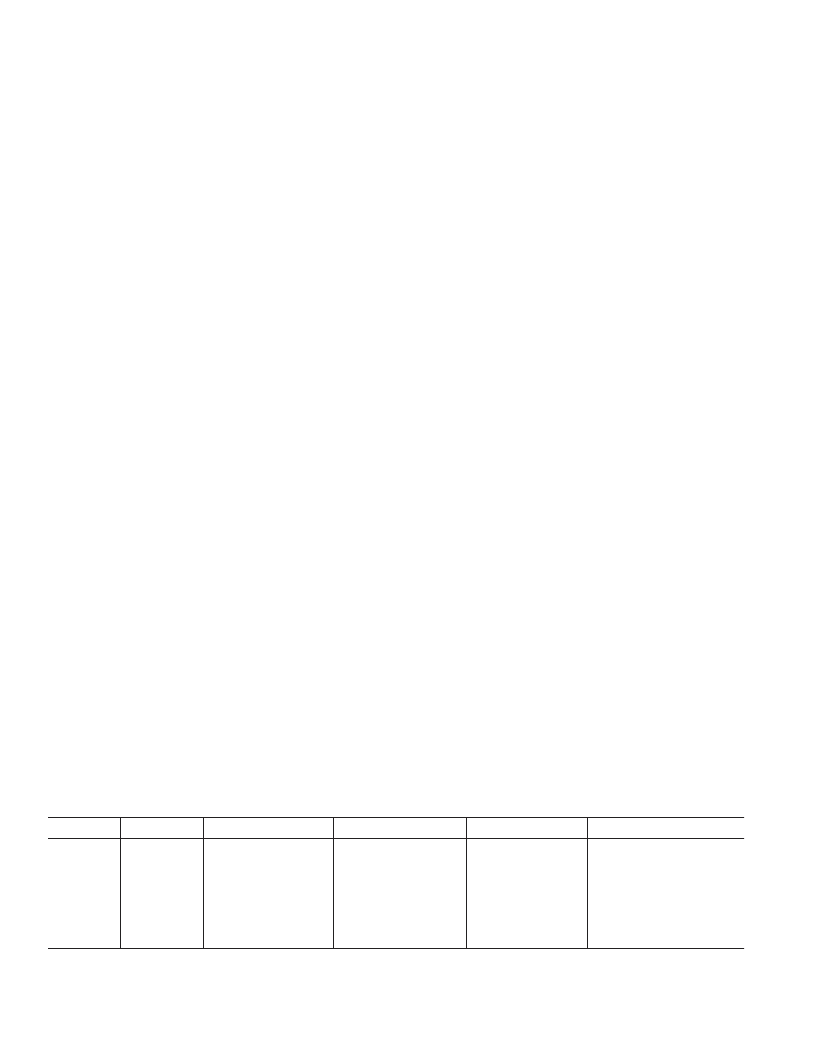

Table IV. Partial List of Capacitors and Key Specifications

Value ( F)

ESR (m )

Voltage Rating (V)

Part Number

Manufacturer

Website

10

22

*

22

22

47

68

100

60

35

35

35

25

18

95

6.3

8

8

8

6.3

8

10

NSP100M6.3D2TR

ESRD220M08B

NSP220M8D5TR

EEFFD0K220R

NSP470M6.3D2TR

ESRD680M08B

594D107X_010C2T

NIC Components

Cornell Dubilier

NIC Components

Panasonic

NIC Components

Cornell Dubilier

Vishay

www.niccomp.com

www.cornell-dubilier.com

www.niccomp.com

www.maco.panasonic.co.jp

www.niccomp.com

www.cornell-dubilier.com

www.vishay.com

*

Recommend capacitor in typical application circuit Figure 1.

相關PDF資料 |

PDF描述 |

|---|---|

| FDR840 | P-Channel 2.5V Specified PowerTrench MOSFET |

| FDR840P | P-Channel 2.5V Specified PowerTrench MOSFET |

| FDR842P | P-Channel 1.8V Specified PowerTrench MOSFET |

| FDR844P | P-Channel 1.8V Specified PowerTrench MOSFET |

| FDR8508P | Dual P-Channel, Logic Level, PowerTrench⑩ MOSFET |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| FDW2520C | 制造商:Fairchild Semiconductor Corporation 功能描述:TSSOP-8 COMPLEMENTARY NCH 20V 300AGA |

| FDW2520C | 制造商:Fairchild Semiconductor Corporation 功能描述:MOSFET |

| FDW2520C_08 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Complementary PowerTrench MOSFET |

| FDW2520C_Q | 功能描述:MOSFET PowerTrench RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

| FDW2521C | 功能描述:MOSFET 20V/-20V N/P RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。