- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375780 > FDW2520C (Analog Devices, Inc.) Thermoelectric Cooler Controller PDF資料下載

參數(shù)資料

| 型號: | FDW2520C |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Thermoelectric Cooler Controller |

| 中文描述: | 熱電冷卻器控制器 |

| 文件頁數(shù): | 13/24頁 |

| 文件大?。?/td> | 416K |

| 代理商: | FDW2520C |

REV. C

ADN8830

–13–

Using TEMPOUT to Measure Temperature

The TEMPOUT pin is a voltage that is proportional to the

difference between the target temperature and the measured

thermistor temperature. The full equation for the voltage at

TEMPOUT

is

×

(

TEMPOUT

The voltage range of

TEMPOUT

is 0 V to 3.0 V and is inde-

pendent of power supply voltage.

Setting the Maximum TEC Voltage and Current

The ADN8830 can be programmed for a maximum output volt-

age to protect the TEC. A voltage from 0 V to 1.5 V applied to

the VLIM (Pin 15) input to the ADN8830 sets the maximum

TEC voltage, V

TEC, MAX

. This voltage can be set with either a

resistor divider or from a DAC. Because the output of the

ADN8830 is bidirectional, this voltage sets both the upper

and lower limits of the TEC voltage. The equation governing

V

TEC, MAX

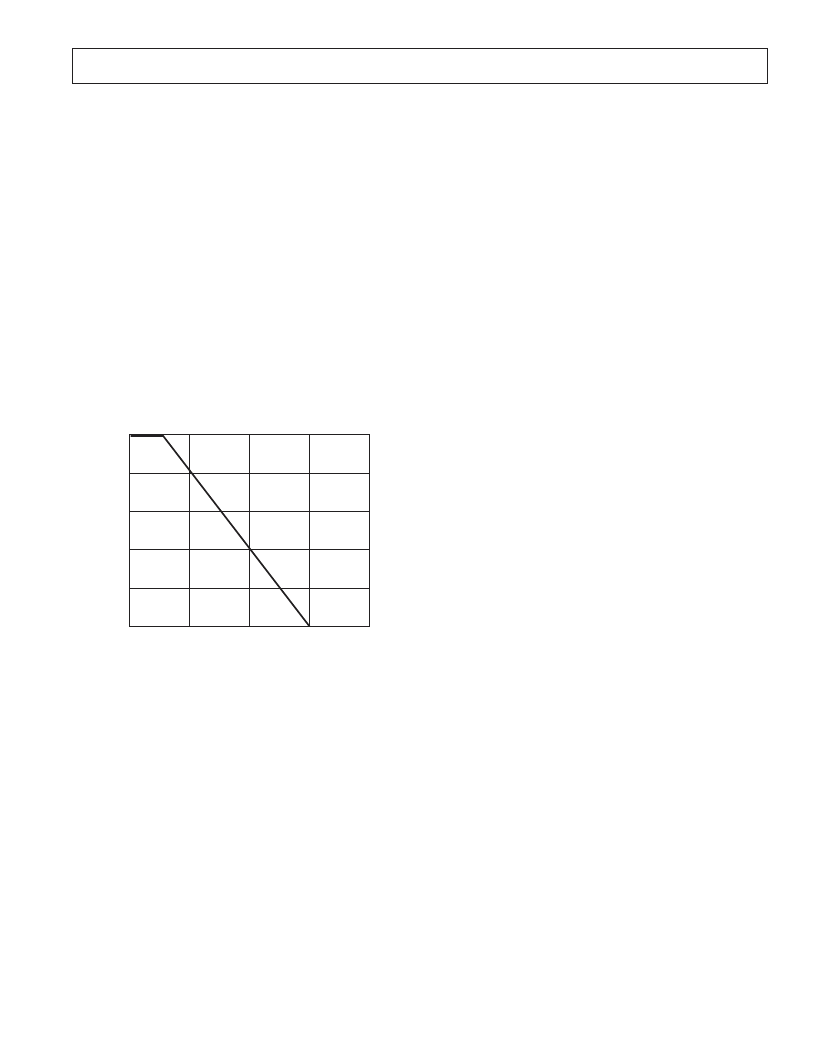

is given in Equation 17 and the graph of this equation

is shown in Figure 12.

=

(

THERMIN

TEMPSET

=

+

)

1 5

.

3

–

(16)

V

V

VLIM

TEC MAX

,

.

–

)

×

1 5

4

(17)

VLIM (V)

5

00

2.0

0.5

V

T

(

1.0

1.5

4

3

2

1

Figure 12. VLIM Voltage vs. Maximum TEC Voltage

If the supply voltage is lower than V

TEC, MAX

, the maximum TEC

voltage will obviously be equal to the supply voltage. The voltage

to VLIM should not exceed 1.5 V since this causes improper

operation of the output voltage limiting circuitry. Setting VLIM to

1.5 V can be used to deactivate the TEC current without

shutting down the ADN8830 in the event of a system failure. If a

maximum TEC voltage is not required, VLIM should be con-

nected to ground. It is not advisable to leave VLIM floating as

this would cause unpredictable output behavior.

This feature should be used to limit the maximum output current

to the TEC as specified in the TEC data sheet. For example, if

the maximum TEC voltage is specified at 2 V, VLIM should be

±

2 V.

Output Driver Amplifiers

The output voltage across the TEC as measured from Pin 19 to

Pin 9 can be monitored at Pin 16. This is labeled as VTEC in

the typical application schematic in Figure 1. The voltage at

VTEC can vary from 0 V to 3 V independent of the power

supply voltage. Its equation is given as

×

(

VTEC

V

V

OUT A

OUT B

=

)

+

0 25

.

1 5

.

–

(18)

where

V

OUT A

and

V

OUT B

are the voltages at Pins 19 and 9, respec-

tively. The ripple voltage at Pin 19 is filtered out internally and

does not appear at VTEC, leaving it as an accurate dc output of

the TEC voltage.

The TEC is driven with a differential voltage, allowing current

to flow in either direction through the TEC. This can provide

heat transfer either to or from the object being regulated without

the use of a negative voltage rail. The maximum output voltage

across the TEC is set by the voltage at VLIM (Pin 15). Refer to

the Setting the Maximum TEC Voltage and Current section for

details on this operation. With VLIM set to ground, the maximum

output voltage is the power supply voltage, V

DD

.

To achieve a differential output, the ADN8830 has two separate

output stages. OUT A is a switched output or pulse-width

modulated (PWM) amplifier, and OUT B is a high gain linear

amplifier. Although they achieve the same result, to provide

constant voltage and high current, their operation is different.

The exact equations for the two outputs are

×

(

×

(

–

14

where

COMPOUT

is the voltage at Pin 13. The voltage at

COMPOUT

is determined by the compensation network that is

fed by the input amplifier, which receives its input voltage from

TEMPSET and THERMIN. Equation 20 is valid only in the

linear region of the linear amplifier. OUT B has a lower limit of

0 V and an upper limit of the power supply.

Because the COMPOUT voltage is not readily known, Equa-

tion 20 can be rewritten in terms of the TEC voltage, VTEC,

which is defined as OUT B

–

OUT A.

VTEC

=

×

+

4

1 5

OUT A

COMPOUT

OUT B

=

)

+

1 5

–

.

(19)

OUT B

COMPOUT

=

)

+

–

.

1 5

.

1 5

(20)

OUT B

(21)

In Figure 1, Pins 10 and 11 provide the gate drive for Q3 and Q4,

which complete the linear output amplifier. This output voltage

is fed back to Pin 9 (OUT B) to close its loop. The gate-to-drain

capacitance of Q3 and Q4 provide the compensation for the

linear amplifier. If using the recommended FDW2520C transistors,

it will be necessary to add an additional 2.2 nF of capacitance

from the gate to the drain of the PMOS transistor to maintain

stability. A 3.3 nF capacitor should also be connected from the

drain to ground to prevent small oscillations when there is very

little or no current through the TEC.

These extra capacitors are specified only when using FDW2520C

transistors in the linear amplifier. If other transistors are used,

these values may need to be adjusted. To ensure the linear

amplifier is stable, the total gate-to-source capacitance for both

Q3 and Q4 should be at least 2.5 nF. Refer to the transistor

’

s

data sheet for its typical gate-to-drain capacitance values.

The output of the linear amplifier is proportional to the voltage

at Pin 13 (COMPOUT). Because the linear amplifier operates

with a gain of 14, its output will typically be at either ground or

V

DD

if there is more than about 100 mA of current flowing

through the TEC. This ensures Q3 and Q4 will not be a domi-

nant source of power dissipation at high output currents.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FDR840 | P-Channel 2.5V Specified PowerTrench MOSFET |

| FDR840P | P-Channel 2.5V Specified PowerTrench MOSFET |

| FDR842P | P-Channel 1.8V Specified PowerTrench MOSFET |

| FDR844P | P-Channel 1.8V Specified PowerTrench MOSFET |

| FDR8508P | Dual P-Channel, Logic Level, PowerTrench⑩ MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FDW2520C | 制造商:Fairchild Semiconductor Corporation 功能描述:TSSOP-8 COMPLEMENTARY NCH 20V 300AGA |

| FDW2520C | 制造商:Fairchild Semiconductor Corporation 功能描述:MOSFET |

| FDW2520C_08 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Complementary PowerTrench MOSFET |

| FDW2520C_Q | 功能描述:MOSFET PowerTrench RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

| FDW2521C | 功能描述:MOSFET 20V/-20V N/P RoHS:否 制造商:STMicroelectronics 晶體管極性:N-Channel 汲極/源極擊穿電壓:650 V 閘/源擊穿電壓:25 V 漏極連續(xù)電流:130 A 電阻汲極/源極 RDS(導(dǎo)通):0.014 Ohms 配置:Single 最大工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:Max247 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。