- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9753 > DS21448LN+ (Maxim Integrated Products)IC LIU QUAD E1/T1/J1 128-LQFP PDF資料下載

參數(shù)資料

| 型號: | DS21448LN+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 38/60頁 |

| 文件大小: | 0K |

| 描述: | IC LIU QUAD E1/T1/J1 128-LQFP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 72 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 4/4 |

| 規(guī)程: | T1/E1/J1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-LQFP(14x20) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

DS21448 3.3V T1/E1/J1 Quad Line Interface

43 of 60

8. JTAG BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT

The DS21448 IEEE 1149.1 design supports the standard instruction codes SAMPLE/PRELOAD, BYPASS, and

EXTEST. Optional public instructions included are HIGHZ, CLAMP, and IDCODE (Table 8-A). The DS21448

contains the following items, which meet the requirements set by the IEEE 1149.1 Standard Test Access Port

(TAP) and Boundary Scan Architecture:

Test Access Port

TAP Controller

Instruction Register

Bypass Register

Boundary Scan Register

Device Identification Register

The TAP has the necessary interface pins JTRST, JTCLK, JTMS, JTDI, and JTDO. See the pin descriptions in

Section 1 for details. Details on Boundary Scan Architecture and the Test Access Port can be found in IEEE

1149.1-1990, IEEE 1149.1a-1993, and IEEE 1149.1b-1994.

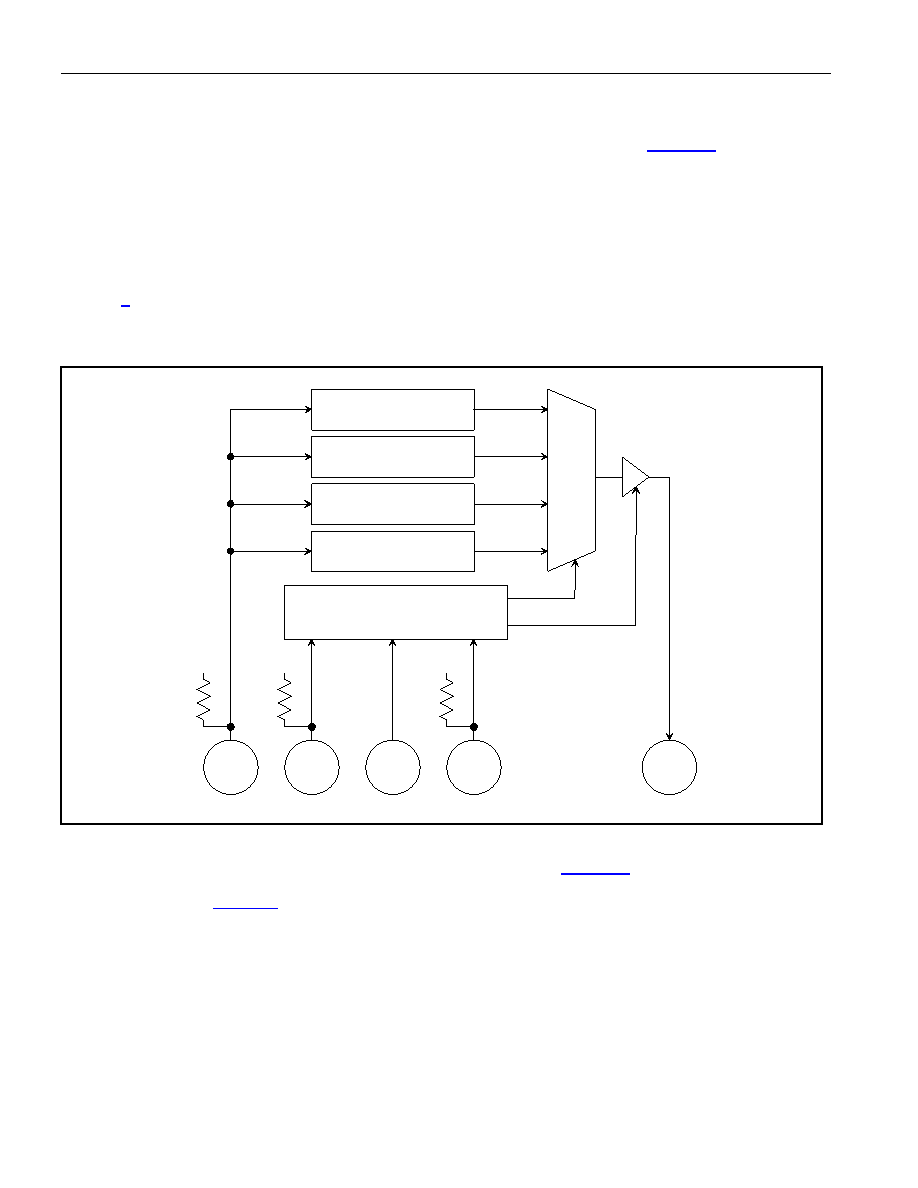

Figure 8-1. JTAG Block Diagram

8.1 JTAG TAP Controller State Machine

This section covers the operation of the TAP controller state machine. See Figure 8-2 for details on each of the

states described below. The TAP controller is a finite state machine that responds to the logic level at JTMS on the

rising edge of JTCLK (Table 8-B).

Test-Logic-Reset. Upon power-up, the TAP controller is in test-logic-reset state. The instruction register contains

the IDCODE instruction. All system logic of the device operates normally.

Run-Test-Idle. The run-test-idle is used between scan operations or during specific tests. The instruction register

and test registers remain idle.

Select-DR-Scan. All test registers retain their previous state. With JTMS LOW, a rising edge of JTCLK moves the

controller into the capture-DR state and initiates a scan sequence. JTMS HIGH during a rising edge on JTCLK

moves the controller to the select-IR-scan state.

JTDI

JTMS

JTCLK

JTRST

JTDO

TEST ACCESS PORT

CONTROLLER

VDD

BOUNDRY SCAN

REGISTER

BYPASS

REGISTER

INSTRUCTION

REGISTER

IDENTIFICATION

REGISTER

MUX

SELECT

OUTPUT ENABLE

10k

10k

10k

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NB7VPQ16MMNHTBG | IC CML DVR PRE-EMPH 1CH 16-QFN |

| MAX1112CPP+ | IC ADC 8BIT LP 20-DIP |

| MS27474T22B21SC | CONN RCPT 21POS JAM NUT W/SCKT |

| MAX1110EPP+ | IC ADC 8BIT LP 20-DIP |

| MS27468T23A35SB | CONN RCPT 100POS JAM NUT W/SCKT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21448LN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448-LW | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21448N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 3.3V E1/T1/J1 Quad Interface RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS2145 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| DS21455 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad E1-T1-J1 Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。