- 您現在的位置:買賣IC網 > PDF目錄375361 > ASDP-21365BBCZ-1AA (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數資料

| 型號: | ASDP-21365BBCZ-1AA |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PBGA136 |

| 封裝: | MO-205AE, BGA-136 |

| 文件頁數: | 5/52頁 |

| 文件大小: | 1320K |

| 代理商: | ASDP-21365BBCZ-1AA |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADSP-21362/ADSP-21363/ADSP-21364/ADSP-21365/ADSP-21366

Rev. A

|

Page 5 of 52

|

December 2006

SHARC FAMILY CORE ARCHITECTURE

The ADSP-2136x is code-compatible at the assembly level with

the ADSP-2126x, ADSP-21160, and ADSP-21161, and with the

first generation ADSP-2106x SHARC processors. The

ADSP-2136x shares architectural features with the ADSP-2126x

and ADSP-2116x SIMD SHARC processors, as detailed in the

following sections.

SIMD Computational Engine

The ADSP-2136x contains two computational processing ele-

ments that operate as a single-instruction multiple-data (SIMD)

engine. The processing elements are referred to as PEX and PEY

and each contains an ALU, multiplier, shifter, and register file.

PEX is always active, and PEY may be enabled by setting the

PEYEN mode bit in the MODE1 register. When this mode is

enabled, the same instruction is executed in both processing ele-

ments, but each processing element operates on different data.

This architecture is efficient at executing math intensive signal

processing algorithms.

Entering SIMD mode also has an effect on the way data is trans-

ferred between memory and the processing elements. When in

SIMD mode, twice the data bandwidth is required to sustain

computational operation in the processing elements. Because of

this requirement, entering SIMD mode also doubles the

bandwidth between memory and the processing elements.

When using the DAGs to transfer data in SIMD mode, two data

values are transferred with each access of memory or the regis-

ter file.

Independent, Parallel Computation Units

Within each processing element is a set of computational units.

The computational units consist of an arithmetic/logic unit

(ALU), multiplier, and shifter. These units perform all opera-

tions in a single cycle. The three units within each processing

element are arranged in parallel, maximizing computational

throughput. Single multifunction instructions execute parallel

ALU and multiplier operations. In SIMD mode, the parallel

ALU and multiplier operations occur in both processing

elements. These computation units support IEEE 32-bit

single-precision floating-point, 40-bit extended-precision

floating-point, and 32-bit fixed-point data formats.

Data Register File

A general-purpose data register file is contained in each pro-

cessing element. The register files transfer data between the

computation units and the data buses, and store intermediate

results. These 10-port, 32-register (16 primary, 16 secondary)

register files, combined with the ADSP-2136x enhanced

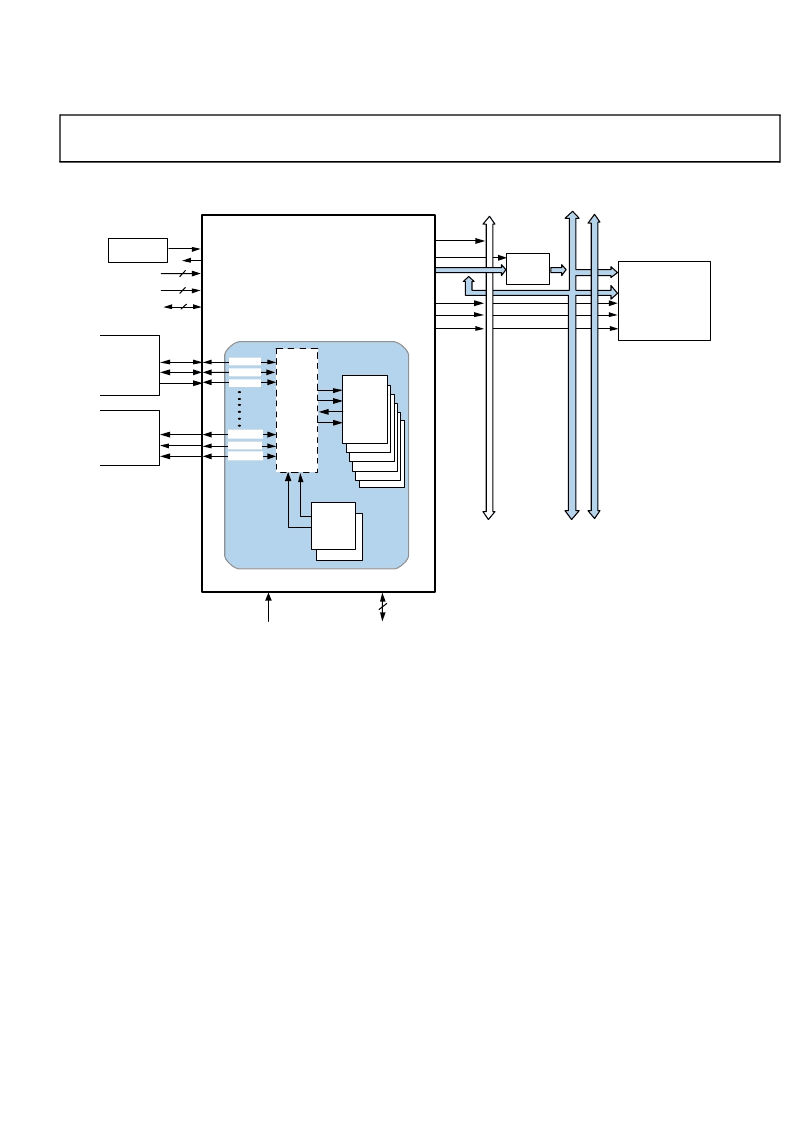

Figure 2. ADSP-2136x System Sample Configuration

DAI

SPI

IDP

SSRC

SPORT0-5

TIMERS

SCLK0

SFS0

SD0A

SD0B

SRU

DAI_P1

DAI_P2

DAI_P3

DAI_P18

DAI_P19

DAI_P20

DAC

(OPTIONAL)

ADC

(OPTIONAL)

FS

CLK

SDAT

FS

CLK

SDAT

3

CLOCK

FLAG3-1

2

2

CLKIN

XTAL

CLK_CFG1-0

BOOTCFG1-0

ADDR

PARALLEL

PORT

RAM

I/O DEVICE

OE

WE

CS

DATA

RD

WR

CLKOUT

ALE

AD15-0

LATCH

RESET

JTAG

6

ADSP-2136x

A

D

C

FLAG0

PCGB

PCGA

CLK

FS

相關PDF資料 |

PDF描述 |

|---|---|

| ASDP-21365KBC-1AA | SHARC Processor |

| ASDP-21365KBCZ-1AA | SHARC Processor |

| ASDP-21365WBBCZ-1A | SHARC Processor |

| ASG509A | CMOS 4/8 CHAANNEL ANALOG MULTIPLEXERS |

| ASI-DDC4563-24 | SILICON DETECTOR DIODE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ASDP-21365KBC-1AA | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ASDP-21365KBCZ-1AA | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ASDP-21365WBBCZ-1A | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ASD-PL2F | 制造商:GAMEWELL-FCI 制造商全稱:GAMEWELL-FCI 功能描述:Analog, addressable photoelectronic smoke sensor |

| ASD-PTL2F | 制造商:GAMEWELL-FCI 制造商全稱:GAMEWELL-FCI 功能描述:Analog, addressable photoelectronic smoke sensor |

發(fā)布緊急采購,3分鐘左右您將得到回復。