- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374047 > ADV7320 (Analog Devices, Inc.) Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7320 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| 中文描述: | 多格式視頻編碼器216兆赫六噪聲整形的12位DAC |

| 文件頁(yè)數(shù): | 80/88頁(yè) |

| 文件大?。?/td> | 1002K |

| 代理商: | ADV7320 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)當(dāng)前第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)

ADV7320/ADV7321

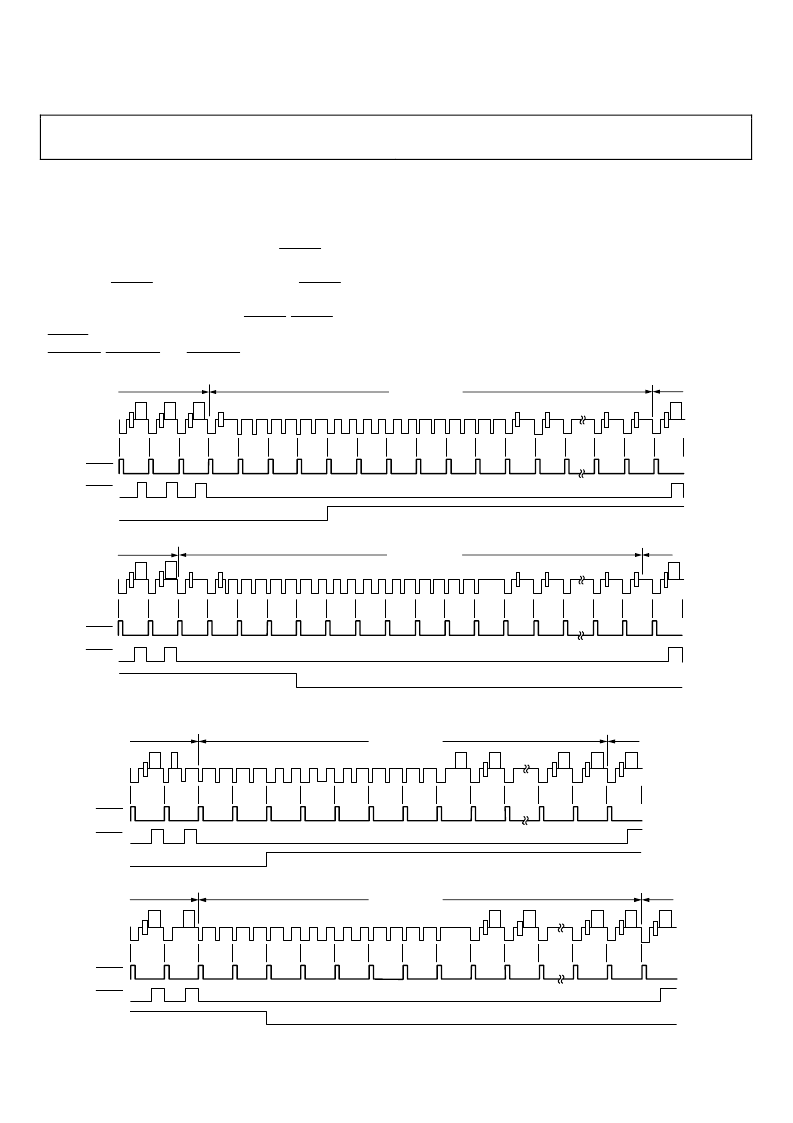

MODE 3—MASTER/SLAVE OPTION

(TIMING REGISTER 0 TR0 =

X X X X X 1 1 0 OR X X X X X 1 1 1)

In this mode, the ADV7320/ADV7321 accept or generate hori-

zontal sync and odd/even field signals. When HSYNC is high, a

transition of the field input indicates a new frame, i.e., vertical

retrace. The BLANK signal is optional. When the BLANK input

is disabled, ADV7320/ADV7321 automatically blank all

normally blank lines as per CCIR-624. HSYNC, BLANK, and

VSYNC are output in master mode and input in slave mode on

S_VSYNC, S_BLANK, and S_VSYNC, respectively.

Rev. 0 | Page 80 of 88

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

283

284

285

ODD FIELD

EVEN FIELD

DISPLAY

DISPLAY

VERTICAL BLANK

522

523

524

525

9

10

11

20

21

22

DISPLAY

DISPLAY

VERTICAL BLANK

ODD FIELD

EVEN FIELD

HSYNC

BLANK

FIELD

0

HSYNC

BLANK

FIELD

8

7

6

5

4

3

2

1

Figure 120. SD Timing Mode 3 (NTSC)

622

623

624

625

5

6

21

22

23

DISPLAY

VERTICAL BLANK

ODD FIELD

EVEN FIELD

FIELD

DISPLAY

309

310

311

312

313

314

315

316

317

318

319

334

335

336

DISPLAY

VERTICAL BLANK

ODD FIELD

EVEN FIELD

FIELD

DISPLAY

320

4

3

2

1

7

HSYNC

BLANK

HSYNC

BLANK

0

Figure 121. SD Timing Mode 3 (PAL)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7321 | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV7321KSTZ | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV7324 | Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| ADV7324KSTZ | Multiformat 216 MHz Video Encoder with Six NSV 14-Bit DACs |

| ADV7340 | Multiformat Video Encoder, Six 12-Bit Noise Shaped Video㈢ DACS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV73205705 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73205706 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73205753 | 制造商:LG Corporation 功能描述:Frame Assembly |

| ADV73207202 | 制造商:LG Corporation 功能描述:Frame Assembly,Door |

| ADV73207203 | 制造商:LG Corporation 功能描述:FRAME ASSEMBLY,DOOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。