- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374016 > ADM9240 (Analog Devices, Inc.) Low Cost Microprocessor System Hardware Monitor PDF資料下載

參數(shù)資料

| 型號: | ADM9240 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Low Cost Microprocessor System Hardware Monitor |

| 中文描述: | 低成本的微處理器系統(tǒng)硬件監(jiān)視器 |

| 文件頁數(shù): | 20/22頁 |

| 文件大?。?/td> | 280K |

| 代理商: | ADM9240 |

ADM9240

–20–

REV. 0

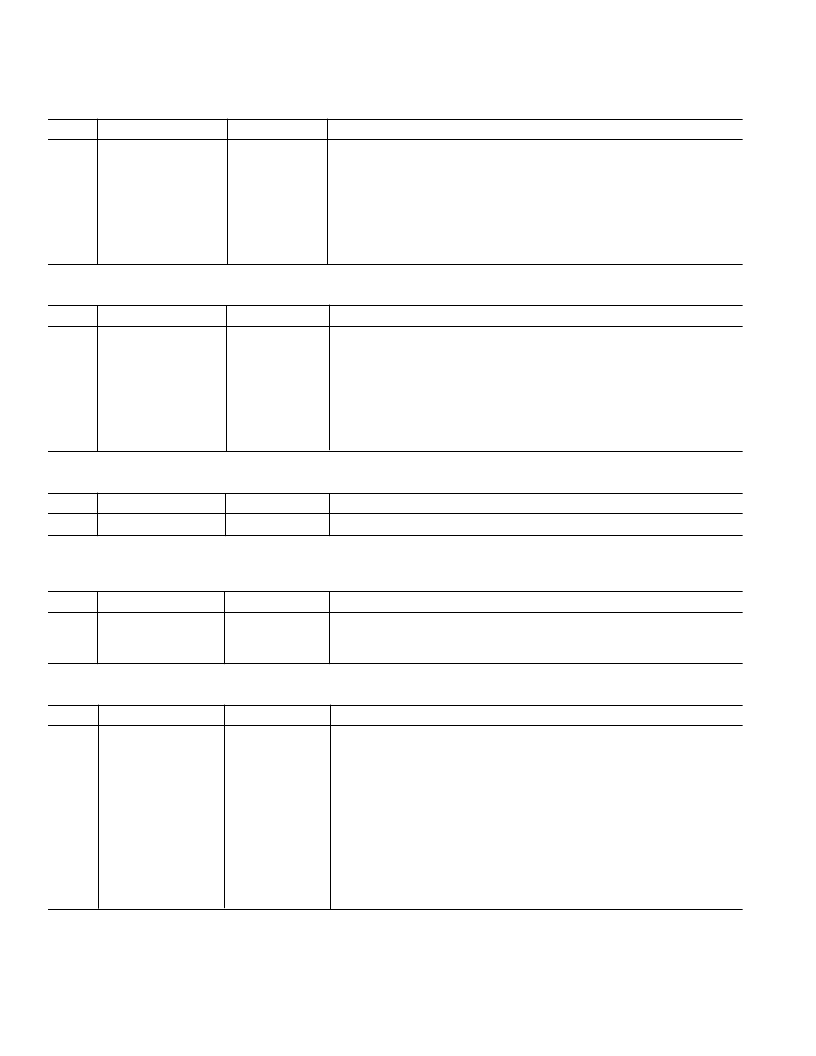

T able X . Register 43h,

INT

Interrupt Mask Register 1 (Power-On Default = 00h)

Bit

Name

R/

W

Description

0

1

2

3

4

5

6

7

+2.5 V

+V

CCP1

+3.3 V

+5 V

T emp

Reserved

FAN1

FAN2

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

Power-On Default = 0.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

T able X I. Register 44h,

INT

Mask Register 2 (Power-On Default = 00h)

Bit

Name

R/

W

Description

0

1

2

3

4

5

6

7

+12 V

V

CCP2

Reserved

Reserved

CI

Reserved

Reserved

RESET

Enable

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

Read/

Write

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

Power-up default set to Low.

Power-up default set to Low.

A “1” disables the corresponding interrupt status bit for

INT

interrupt.

Undefined.

Undefined.

A “1” enables the

RESET

function in the configuration register.

T able X II. Register 45h, Reserved Compatibility (Power-On Default = 00h)

Bit

Name

R/

W

Description

0–7

Reserved

Read/

Write

Reserved for Compatibility.

T able X III. Register 46h, Chassis Intrusion Clear (Power-On Default = 00h)

Bit

Name

R/

W

Description

0–6

7

Reserved

Chassis Int. Clear

Read/

Write

Read/

Write

Undefined (Power On Default = 00h)

A “1” outputs a minimum 20 ms active low pulse on the chassis intrusion

pin. T he register bit clears itself after the pulse has been output.

T able X IV. Register 47h, VID0–3/Fan Divisor Register (Power-On Default 0101(VID3–VID0))

Bit

Name

R/

W

Description

0–3

VID

Read

T he VID[3:0] inputs from processor core power supplies to indicate the

operating voltage (e.g., 1.3 V to 3.5 V).

Sets Counter Prescaler for FAN1 Speed Measurement

<5:4> = 00 – Divide by 1

<5:4> = 01 – Divide by 2

<5:4> = 10 – Divide by 4

<5:4> = 11 – Divide by 8

Sets Counter Prescaler for FAN2 Speed Measurement

<7:6> = 00 – Divide by 1

<7:6> = 01 – Divide by 2

<7:6> = 10 – Divide by 4

<7:6> = 11 – Divide by 8

4–5

FAN1 Divisor

Read/

Write

6–7

FAN2 Divisor

Read/

Write

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADM9240ARU | Low Cost Microprocessor System Hardware Monitor |

| ADM9261 | Triple- Power Supply Monitor(3路電源監(jiān)視器) |

| ADM9264ARN-REEL | Quad Power Supply Monitor for Desktop PCs |

| ADM9264ARN-REEL7 | Quad Power Supply Monitor for Desktop PCs |

| ADM9264 | Quad Power Supply Monitor for Desktop PCs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADM9240ARU | 制造商:Analog Devices 功能描述:Data Acquisition System, 6 Channel, 9 Bit, 24 Pin, Plastic, TSSOP |

| ADM9240ARU-REEL | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost Microprocessor System Hardware Monitor |

| ADM9240ARU-REEL7 | 制造商:Analog Devices 功能描述: |

| ADM9264 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad Power Supply Monitor for Desktop PCs |

| ADM9264ARN | 制造商:Analog Devices 功能描述:Volt Supervisor Monitor 2.8V/3.3V/5V/12V 16-Pin SOIC N 制造商:Rochester Electronics LLC 功能描述:MULTI-SUPPLY HARDWARE MON - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。