- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1895 > AD9980KSTZ-95 (Analog Devices Inc)IC INTERFACE 8BIT ANALOG 80LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AD9980KSTZ-95 |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 16/44頁(yè) |

| 文件大小: | 0K |

| 描述: | IC INTERFACE 8BIT ANALOG 80LQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 應(yīng)用: | 視頻 |

| 接口: | 模擬 |

| 電源電壓: | 3.13 V ~ 3.47 V |

| 封裝/外殼: | 80-LQFP |

| 供應(yīng)商設(shè)備封裝: | 80-LQFP(14x14) |

| 包裝: | 管件 |

| 安裝類(lèi)型: | 表面貼裝 |

| 配用: | AD9980/PCBZ-ND - KIT EVALUATION AD9980 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

AD9980

Rev. 0 | Page 23 of 44

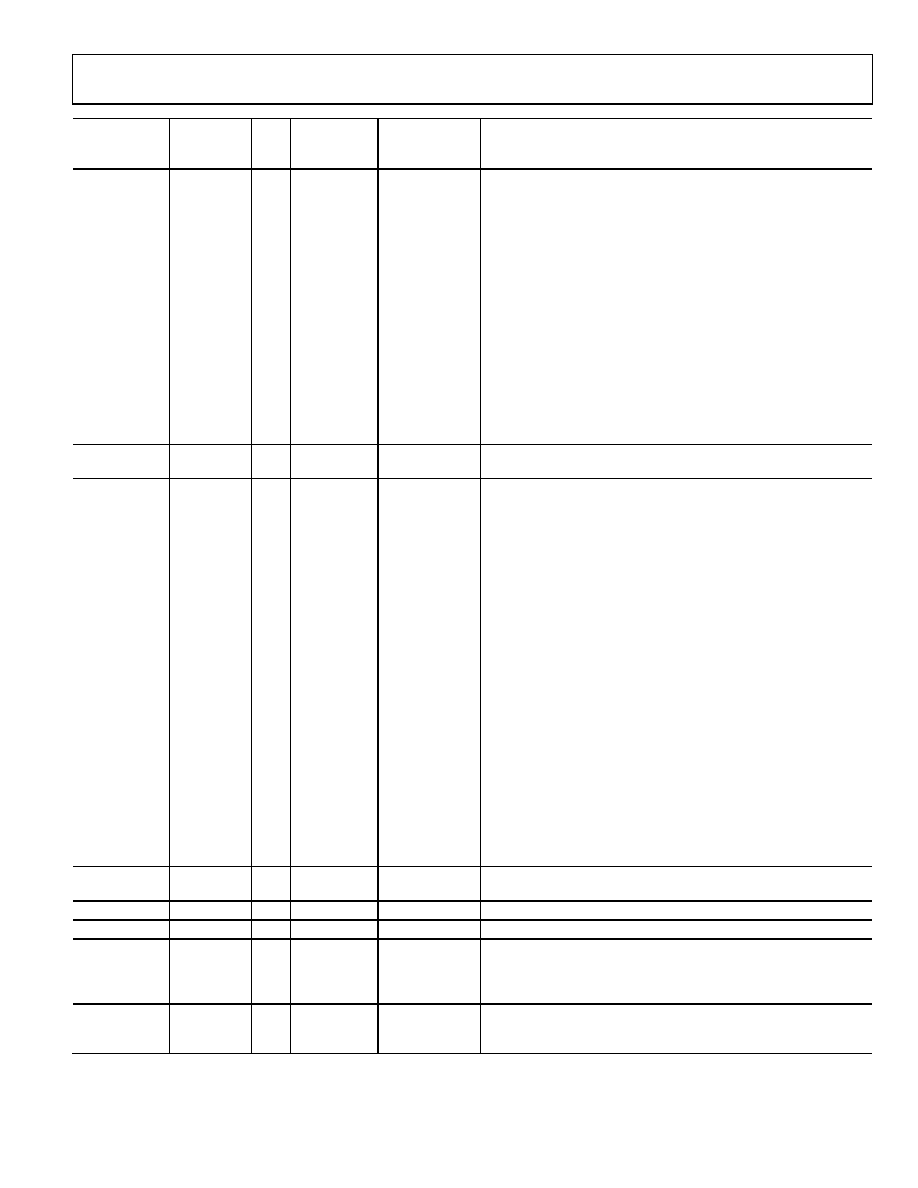

Hexadecimal

Address

Read and

Write or

Read Only

Bits

Default

Value

Register

Name

Description

0x12

R/W

7

0*** ****

Hsync Control

Active Hsync Override.

0 = The chip determines the active Hsync source.

1 = The active Hsync Source is set by 0x12, Bit 6.

6

*0** ****

Selects the source of the Hsync for PLL and sync processing. This

bit is used only if 0x12, Bit 7 is set to 1 or if both syncs are active.

0 = Hsync is from Hsync input pin.

1 = Hsync is from SOG.

5

**0* ****

Hsync Polarity Override.

0 = The chip selects the Hsync input polarity.

1 = The polarity of the input Hsync is controlled by 0x12, Bit 4.

This applies to both Hsync0 and Hsync1.

4

***1 ****

Hsync input polarity: this bit is used only if 0x12, Bit 5 is set to 1.

0 = Active low input Hsync.

1 = Active high input Hsync.

3

**** 1***

Sets the polarity of the Hsync output signal.

0 = Active low Hsync output.

1 = Active high Hsync output.

0x13

R/W

7:0

0010 0000

Hsync

Duration

Sets the number of pixel clocks that Hsync out is active.

0x14

R/W

7

0*** ****

Vsync Control

Active Vsync Override.

0 = The chip determines the active Vsync source.

1 = The active Vsync source is set by 0x14, Bit 6.

6

*0** ****

Selects the source of Vsync for the sync processing. This bit is used

only if 0x14, Bit 7 is set to 1.

0 = Vsync is from the Vsync input pin.

1 = Vsync is from the sync separator.

5

**0* ****

Vsync Polarity Override.

0 = The chip selects the input Vsync polarity.

1 = The polarity of the input Vsync is set by 0x14, Bit 4.

This applies to both Vsync0 and Vsync1.

4

***1 ****

Vsync input polarity: this bit is used only if 0x14, Bit 5 is set to 1.

0 = Active low input Vsync.

1 = Active high input Vsync.

3

**** 1***

Sets the polarity of the output Vsync signal.

0 = Active low output Vsync.

1 = Active high output Vsync.

2

**** *0**

0 = The Vsync filter is disabled.

1 = The Vsync filter is enabled.

This needs to be enabled when using the Hsync to Vsync counter.

1

**** **0*

Enables the Vsync duration block. This is designed to be used with

the Vsync filter.

0 = Vsync output duration is unchanged.

1 = Vsync output duration is set by Register 0x15.

0x15

R/W

7:0

0000 1010

Vsync Duration

Sets the number of Hsyncs that Vsync out is active. This is only

used if 0x14, Bit 1 is set to 1.

0x16

R/W

7:0

0000 0000

Precoast

The number of Hsync periods to Coast prior to Vsync.

0x17

R/W

7:0

0000 0000

Postcoast

The number of Hsync periods to Coast after Vsync.

0x18

R/W

7

0*** ****

Coast and

Clamp Control

Coast Source.

Selects the source of the Coast signal.

0 = Using internal Coast generated from Vsync.

1 = Using external Coast signal from external COAST pin.

6

*0** ****

Coast Polarity Override.

0 = The chip selects the external Coast polarity.

1 = The polarity of the external Coast signal is set by 0x18, Bit 5.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9981KSTZ-95 | IC INTERFACE 10BIT ANALOG 80LQFP |

| AD9983AKSTZ-170 | IC DISPLAY 8BIT 170MSPS 80LQFP |

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

| AD9990BBCZ | IC CCD SGNL PROCESSOR 112CSPBGA |

| AD9991KCPZRL | IC CCD SIGNAL PROCESSOR 56-LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9980KSTZ-RL95 | 制造商:Analog Devices 功能描述: |

| AD9980PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 8-Bit Display Interface |

| AD9981 | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 10-Bit Display Interface |

| AD9981/PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 10-Bit Display Interface |

| AD9981/PCBZ | 制造商:Analog Devices 功能描述:Evaluation Board For The High Performance 10-Bit Display Interface 制造商:Analog Devices 功能描述:EVAL BD FOR THE HI-PERF 10-BIT DISPLAY INTRFC - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。