- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11767 > AD6620ASZ-REEL (Analog Devices Inc)IC DGTL RCVR DUAL 67MSPS 80-PQFP PDF資料下載

參數(shù)資料

| 型號: | AD6620ASZ-REEL |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 41/44頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 標(biāo)準(zhǔn)包裝: | 500 |

| 接口: | 并行/串行 |

| 電源電壓: | 3 V ~ 3.6 V |

| 封裝/外殼: | 80-BQFP |

| 供應(yīng)商設(shè)備封裝: | 80-PQFP(14x14) |

| 包裝: | 帶卷 (TR) |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁

AD6620

–6–

REV. A

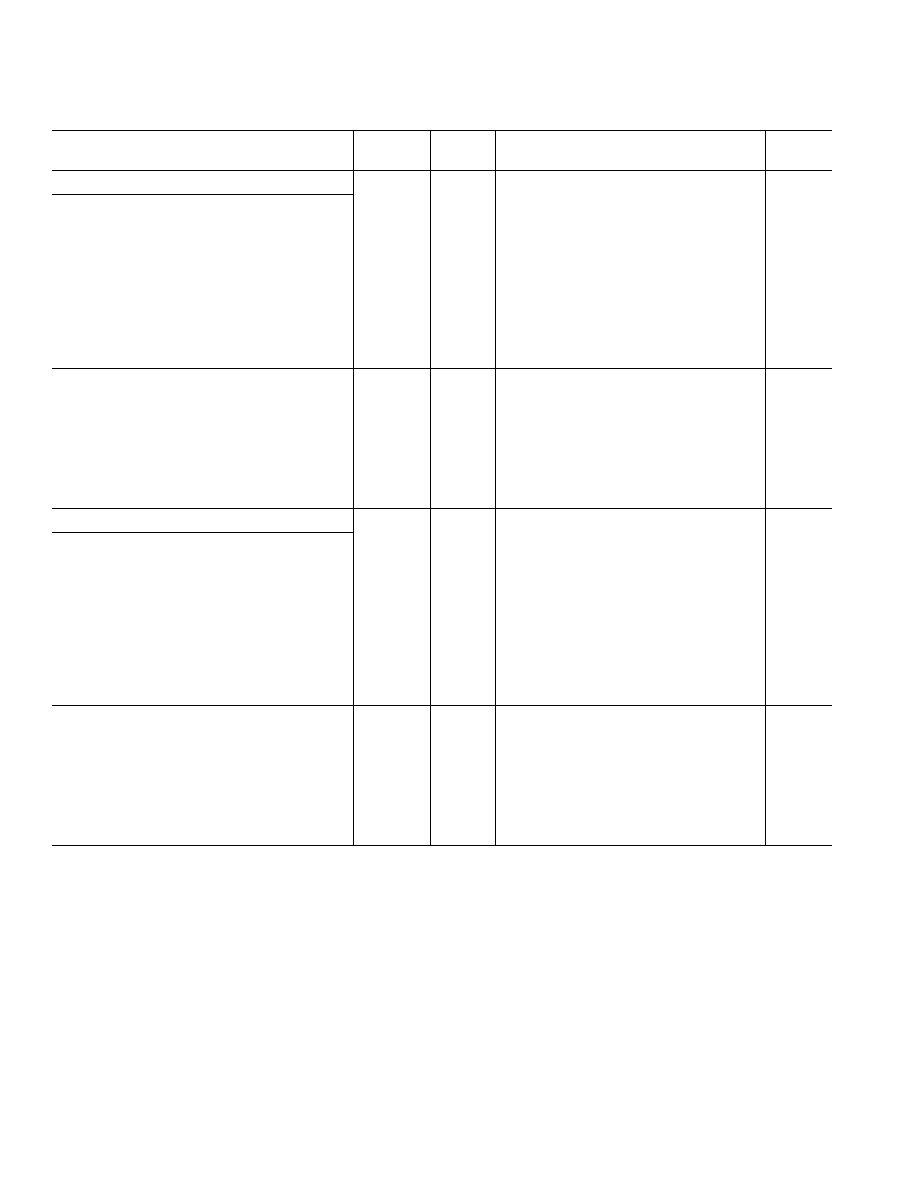

TIMING CHARACTERISTICS (C

LOAD = 40 pF All Outputs)

Test

AD6620AS

Parameter (Conditions)

Temp

Level

Min

Typ

Max

Unit

MICROPROCESSOR PORT, MODE = 0

MODE0 Input Timing Requirements:

tSC

Control

1 to CLK Setup Time

Full

IV

3.0

ns

tHC

Control1 to CLK Hold Time

Full

IV

5.0

ns

tHA

Address

2 to CLK Hold Time

Full

IV

3.0

ns

tZR

CS to Data Enabled Time

Full

IV

5.0

ns

tZD

CS to Data Disabled Time

Full

IV

5.0

ns

tSAM

CS to Address/Data Setup Time

Full

IV

0.0

ns

MODE0 Read Switching Characteristics:

tDD

CLK to Data Valid Time

Full

I

10.0

15.0

30.0

ns

tRDY

RD to RDY Time

Full

IV

4.0

19.5

ns

MODE0 Write Timing Requirements:

tSC

Control

1 to CLK Setup Time

Full

IV

3.0

ns

tHC

Control

1

Full

IV

5.0

ns

tHM

Micro Data

3 to CLK Hold Time

Full

IV

3.0

ns

tHA

Address

2 to CLK Hold Time

Full

IV

3.0

ns

tSAM

Address/Data Setup Time to

CS

Full

IV

0.0

ns

MODE0 Write Switching Characteristics:

tRDY

RD to RDY Time

Full

IV

4.0

19.5

ns

MICROPROCESSOR PORT, MODE = 1

MODE1 Input Timing Requirements:

tSC

Control

1 to CLK Setup Time

Full

IV

3.0

ns

tHC

Control

1 to CLK Hold Time

Full

IV

5.0

ns

tHA

Address2 to CLK Hold Time

Full

IV

3.0

ns

tZR

CS to Data Enabled Time

Full

IV

5.0

ns

tZD

CS to Data Disabled Time

Full

IV

5.0

ns

tSAM

Address/Data Setup Time to

CS

Full

IV

0.0

ns

MODE1 Read Switching Characteristics:

tDD

CLK to Data Valid Time

Full

I

10.0

30.0

ns

tDTACK

CLK to DTACK Time

Full

V

5.5

15.5

ns

MODE1 Write Timing Requirements:

tSC

Control

1 to CLK Setup Time

Full

IV

0.0

ns

tHC

Control

1 to CLK Hold Time

Full

IV

5.0

ns

tHM

Micro Data

3 to CLK Hold Time

Full

IV

6.5

ns

tHA

Address

2 to CLK Hold Time

Full

IV

3.0

ns

tSAM

Address/Data Setup Time to

CS

Full

IV

0.0

ns

MODE1 Write Switching Characteristic:

tDTACK

CLK to DTACK Time

Full

V

5.5

15.5

ns

NOTES

1Specification pertains to: R/W (

WR), DS (RD), CS.

2Specification pertains to: A[2:0].

3Specification pertains to: D[7:0].

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 6274291-2 | CONN JACK VERT PCB 75 OHM BNC |

| AD7669JNZ | IC I/O PORT 8BIT ANLG 28DIP |

| D38999/24FF11PA | CONN RCPT 11POS JAM NUT W/PINS |

| D38999/20JE26HN | CONN RCPT 26POS WALL MNT W/PINS |

| AD7569KNZ | IC I/O PORT 8BIT ANALOG 24DIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6620PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全稱:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

| AD6622AS | 制造商:Analog Devices 功能描述:Transmit Signal Processor 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CHANNEL 65 MSPS DIGITAL UPCONVERTER - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。