- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24864 > 950812CGLF (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 950812CGLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, GREEN, MO-153, TSSOP-56 |

| 文件頁數(shù): | 12/31頁 |

| 文件大小: | 285K |

| 代理商: | 950812CGLF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

2

ICS950812

0542H—04/08/05

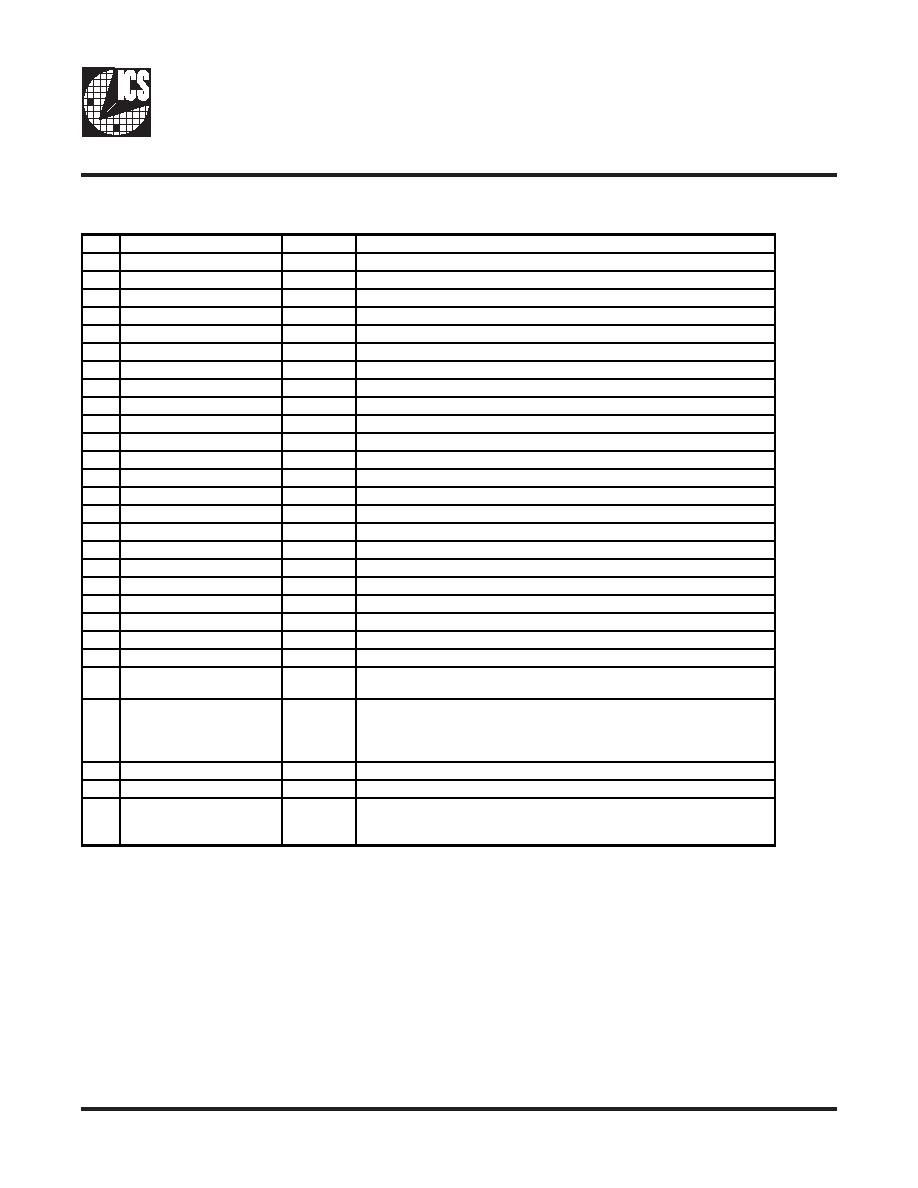

Pin Configuration

PIN # PIN NAME

PIN TYPE

DESCRIPTION

1

VDDREF

PWR

Ref, XTAL power supply, nominal 3.3V

2

X1

IN

Crystal input, Nominally 14.318MHz.

3

X2

OUT

Crystal output, Nominally 14.318MHz

4

GND

PWR

Ground pin.

5

PCICLK_F0

OUT

Free running PCI clock not affected by PCI_STOP# .

6

PCICLK_F1

OUT

Free running PCI clock not affected by PCI_STOP# .

7

PCICLK_F2

OUT

Free running PCI clock not affected by PCI_STOP# .

8

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

9

GND

PWR

Ground pin.

10

PCICLK0

OUT

PCI clock output.

11

**E_PCICLK1/PCICLK1

I/O

Early/Normal PCI clock output latched at power up.

12

PCICLK2

OUT

PCI clock output.

13

**E_PCICLK3/PCICLK3

I/O

Early/Normal PCI clock output latched at power up.

14

VDDPCI

PWR

Power supply for PCI clocks, nominal 3.3V

15

GND

PWR

Ground pin.

16

PCICLK4

OUT

PCI clock output.

17

PCICLK5

OUT

PCI clock output.

18

PCICLK6

OUT

PCI clock output.

19

VDD3V66

PWR

Power pin for the 3V66 clocks.

20

GND

PWR

Ground pin.

21

66MHZ_OUT0/3V66_2

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

22

66MHZ_OUT1/3V66_3

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

23

66MHZ_OUT2/3V66_4

OUT

3.3V 66.66MHz clock output selected via buffered or internal VCO.

24

66MHZ_IN/3V66_5

I/O

3.3V 66.66MHz clock from internal VCO, 66MHZ input to 66MHz output and

PCI.

25

*PD#

IN

Asynchronous active low input pin used to power down the device into a low

power state. The internal clocks are disabled and the VCO and the crystal

are stopped. The latency of the power down will not be greater than 1.8ms.

26

VDDA

PWR

3.3V power for the PLL core.

27

GND

PWR

Ground pin.

28

Vtt_PWRGD#

IN

This 3.3V LVTTL input is a level sensitive strobe used to determine when

latch inputs are valid and are ready to be sampled. This is an active low

input.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08056C103JAT4A | General Specifications |

| 950812YGLFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 950812YGT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 950902DGLFT | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 08056C103JAT7A | Separating plate, width: 0.8 mm, color: gray - TS-GSK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 950812CGLFT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 950812YFLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| 950812YGLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Frequency Generator with 200MHz Differential CPU Clocks |

| 950813 | 制造商:Weidmuller 功能描述:NEXT 74/55/16, 4GP, ST, ZINC -EA - Bulk |

| 9508131 | 制造商:Molex 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。