- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9858 > 78Q2133R/F (Maxim Integrated Products)TXRX 10/100 MDIX 3.3V IND 32-QFN PDF資料下載

參數(shù)資料

| 型號: | 78Q2133R/F |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 4/38頁 |

| 文件大?。?/td> | 0K |

| 描述: | TXRX 10/100 MDIX 3.3V IND 32-QFN |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 2,500 |

| 類型: | PHY 收發(fā)器 |

| 驅(qū)動器/接收器數(shù): | 4/4 |

| 規(guī)程: | IEEE 802 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-VFQFN 裸露焊盤 |

| 供應商設備封裝: | 32-QFN 裸露焊盤(5x5) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

78Q2123/78Q2133 Data Sheet

DS_21x3_001

12

Rev. 1.6

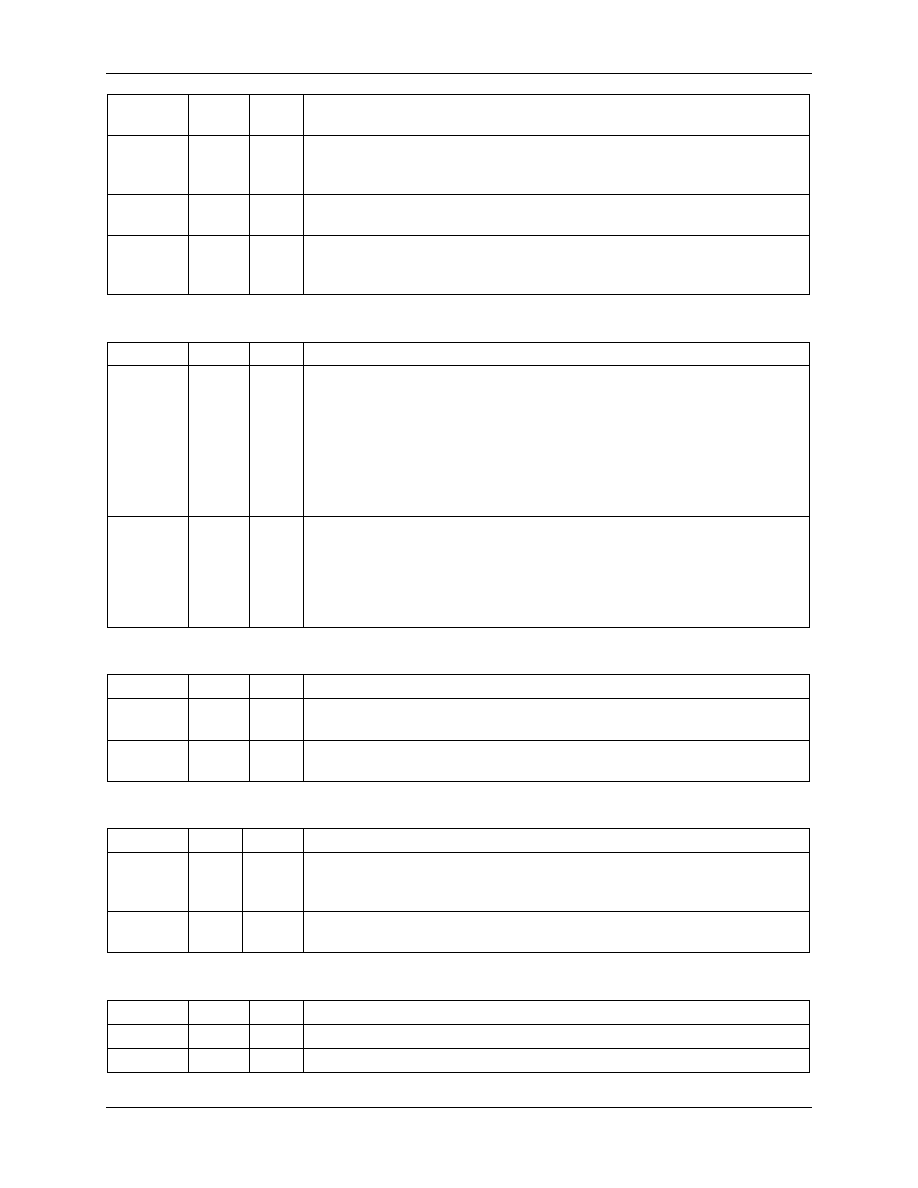

RXD[3:0]

[5:8]

COZ

RECEIVE DATA: Received data is provided to the MAC via RXD[3:0].

These pins are tri-stated in isolate mode.

RX_ER

13

COZ

RECEIVE ERROR: RX_ER is asserted high when an error is detected

during frame reception. In PCS bypass mode, this pin becomes the MSB of

the receive 5-bit code group. This pin is tri-stated in isolate mode.

MDC

2

CIS

MANAGEMENT DATA CLOCK: MDC is the clock used for transferring

data via the MDIO pin.

MDIO

1

CIO

MANAGEMENT DATA INPUT/OUTPUT: MDIO is a bi-directional port

used to access management registers within the 78Q2123/78Q2133. This

pin requires an external pull-up resistor as specified in IEEE-802.3.

2.3

Control and Status

Signal

Pin

Type

Description

RST

23

CIS

ACTIVE LOW RESET: When pulled low the pin resets the chip. The reset

pulse must be long enough to guarantee stabilization of the supply

voltage and startup of the oscillator. Refer to the Electrical Specifications

for the reset pulse requirements. There are two other ways to reset the

chip:

1.

Through the internal power-on-reset (activated when the chip is

being powered up).

2.

Through the MII register bit (MR 0.15).

INTR

32

COZ

INTERRUPT PIN: This pin is used to signal an interrupt to the media

access controller. The pin is held in the high impedance state when an

interrupt is not indicated. The pin will be forced high or low to signal an

interrupt depending upon the value of the INPOL bit (MR16.14). The

events which trigger an interrupt can be programmed via the Interrupt

Control Register located at address MR17.

2.4

MDI (Media Dependent Interface)

Signal

Pin

Type

Description

TXOP,

TXON

30,31

A

TRANSMIT OUTPUT POSITIVE/NEGATIVE: Transmitter differential

outputs for both 10base-T and 100base-TX.

RXIP,

RXIN

28,27

A

RECEIVE INPUT POSITIVE/NEGATIVE: Receiver differential inputs for

both 10BASE-T and 100BASE-TX.

2.5

Oscillator/Clock

Signal

Pin

Type

Description

XTLP

24

A

CRYSTAL INPUT: Should be connected to a 25 MHz crystal. If an

externally generated TTL compatibility clock signal is used, that signal is

applied here.

XTLN

25

A

CRYSTAL OUTPUT: Should be connected to a 25 MHz crystal. When an

external clock source is being used, this pin must be grounded.

2.6

Power Supply and Ground

Signal

Pin

Type

Description

PWR

9, 26

S

+3.3VDC SUPPLY

GND

10, 29

G

GROUND

相關PDF資料 |

PDF描述 |

|---|---|

| MAX3314ECKA+T | IC TXRX RS232 460KBPS SOT23-8 |

| VI-25K-MX-F1 | CONVERTER MOD DC/DC 40V 75W |

| MS27468T11B98SB | CONN RCPT 6POS JAM NUT W/SCKT |

| MS27466P15F18SC | CONN RCPT 18POS WALL MT W/SCKT |

| VI-25J-MX-F3 | CONVERTER MOD DC/DC 36V 75W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 78Q2133S/F | 功能描述:1/1 Transceiver Full Ethernet 32-TQFN (5x5) 制造商:maxim integrated 系列:- 包裝:管件 零件狀態(tài):有效 類型:收發(fā)器 協(xié)議:以太網(wǎng) 驅(qū)動器/接收器數(shù):1/1 雙工:全 接收器滯后:- 數(shù)據(jù)速率:- 電壓 - 電源:3.3V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:32-WFQFN 裸露焊盤 供應商器件封裝:32-TQFN(5x5) 標準包裝:490 |

| 78Q2133SR/F | 功能描述:1/1 Transceiver Full Ethernet 32-TQFN (5x5) 制造商:maxim integrated 系列:- 包裝:帶卷(TR) 零件狀態(tài):有效 類型:收發(fā)器 協(xié)議:以太網(wǎng) 驅(qū)動器/接收器數(shù):1/1 雙工:全 接收器滯后:- 數(shù)據(jù)速率:- 電壓 - 電源:3.3V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:32-WFQFN 裸露焊盤 供應商器件封裝:32-TQFN(5x5) 標準包裝:2,500 |

| 78Q8340-ARM9-EVM | 功能描述:開發(fā)板和工具包 - ARM 700-78Q8340ARM9-EVM- Kit RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| 78Q8392L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Low Power Ethernet Coaxial Transceiver |

| 78Q8392L/A03 | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Low Power Ethernet Coaxial Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復。