- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄18687 > 73S1210F-68MR/F/PH (Maxim Integrated)IC SOC SMART CARD READER 68QFN PDF資料下載

參數(shù)資料

| 型號: | 73S1210F-68MR/F/PH |

| 廠商: | Maxim Integrated |

| 文件頁數(shù): | 71/126頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC SOC SMART CARD READER 68QFN |

| 標(biāo)準(zhǔn)包裝: | 2,500 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當(dāng)前第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

DS_1210F_001

73S1210F Data Sheet

Rev. 1.4

49

1.7.9

User (USR) Ports

The 73S1210F includes 8 pins of general purpose digital I/O (GPIO). On reset or power-up, all USR pins

are inputs until they are configured for the desired direction. The pins are configured and controlled by

or output with the bits of the UDIR70 register. Table 47 lists the direction registers and configurability

associated with each group of USR pins. USR pins 0 to 7 are multiple use pins that can be used for

general purpose I/O, external interrupts and timer control. Table 48 shows the configuration for a USR

pin through its associated bit in its UDIR register. Values read from and written into the GPIO ports use

the data registers USR70. Note: After reset, all USR pins are defaulted as inputs and pulled up to VDD

until any write to the corresponding UDIR register is performed. This insures all USR pins are set to a

known value until set by the firmware. Unused USR pins can be set for output if unused and

unconnected to prevent them from floating. Alternatively, unused USR pins can be set for input and tied

to ground or VDD.

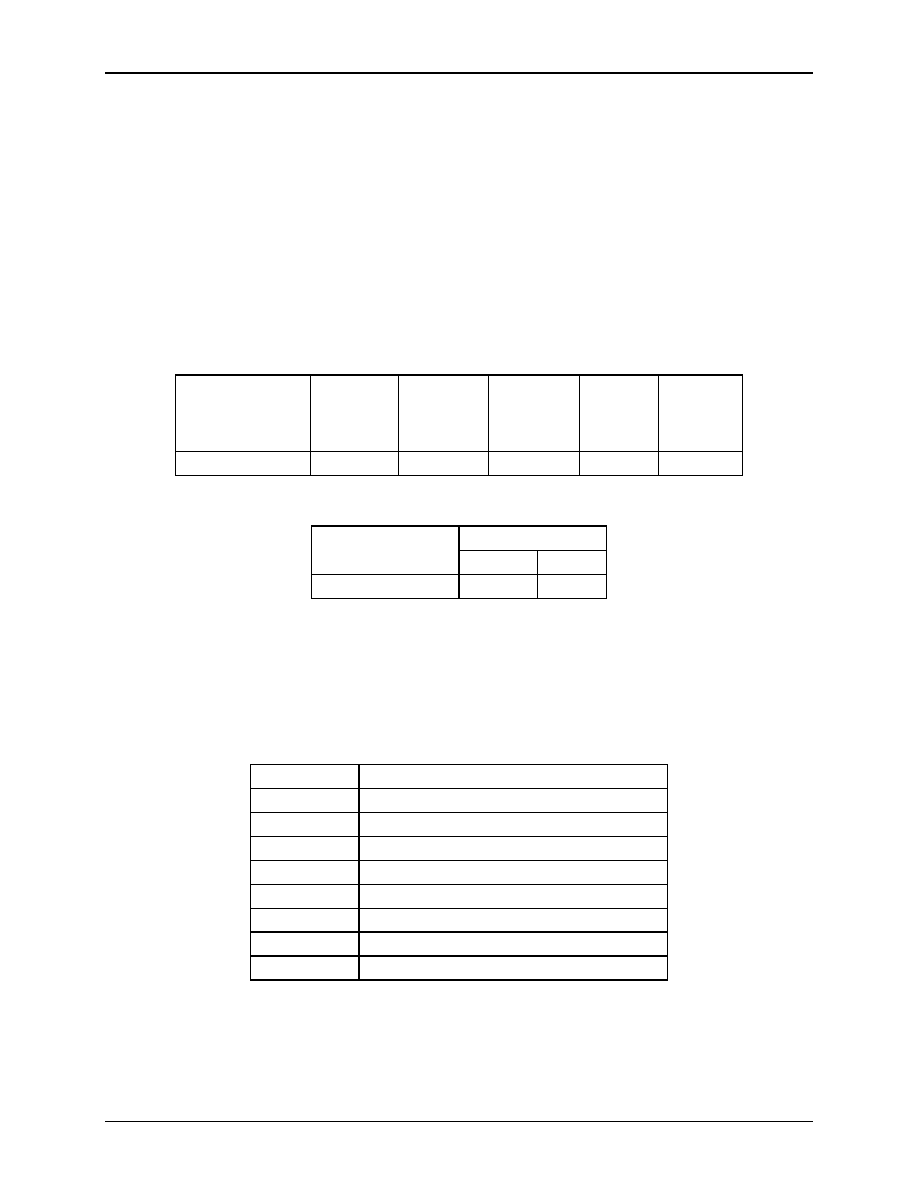

Table 47: Direction Registers and Internal Resources for DIO Pin Groups

USR Pin Group

Type

Direction

Register

Name

Direction

Register

(SFR)

Location

Data

Register

Name

Data

Register

(SFR)

Location

USR_0…USR_7

Multi-use

UDIR70

0x91 [7:0]

USR70

0x90 [7:0]

Table 48: UDIR Control Bit

UDIR Bit

0

1

USR Pin Function

output

input

Four XRAM SFR registers (USRIntTCtl0, USRIntTCtl1, USRIntTCtl2, and USRIntTCtl3) control the use of

the USR [7:0] pins. Each of the USR [7:0] pins can be configured as GPIO or individually be assigned an

internal resource such as an interrupt or a timer/counter control. Each of the four registers contains two

3-bit configuration words named UxIS (where x corresponds to the USR pin). The control resources

selectable for the USR pins are listed in Table 50 through Table 53. If more than one input is connected

to the same resource, the resources are combined using a logical OR.

Table 49: Selectable Controls Using the UxIS Bits

UxIS Value

Resource Selected for USRx Pin

0

None

1

None

2

T0 (counter0 gate/clock)

3

T1 (counter1 gate/clock)

4

Interrupt 0 rising edge/high level on USRx

5

Interrupt 1 rising edge/high level on USRx

6

Interrupt 0 falling edge/low level on USRx

7

Interrupt 1 falling edge/low level on USRx

Note: x denotes the corresponding USR pin. Interrupt edge or level control is assigned in the IT0 and IT1

bits in the TCON register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FQD1N80TM | MOSFET N-CH 800V 1A DPAK |

| 73S1210F-68MR/F/PG | IC SOC SMART CARD READER 68QFN |

| XRCWHT-L1-0000-00601 | LED COOL WHITE 500MA 7X9 SMD |

| 73S1210F-44M/F/PC | IC SOC SMART CARD READER 44QFN |

| XRCWHT-L1-0000-00403 | LED COOL WHITE 500MA 7X9 SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S1210F-EB | 功能描述:開發(fā)板和工具包 - 8051 73S1210F Eval Brd (Doc. Cd, Cable) RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 73S1210F-EB-Lite | 功能描述:開發(fā)板和工具包 - 8051 73S1210F Eval Brd Lite w/Doc Cd, Cable RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 73S1210F-EB-LiteMS | 功能描述:開發(fā)板和工具包 - 8051 73S1210F Eval Brd Lite + Multi Sam RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 73S1215F | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:80515 System-on-Chip with USB, ISO 7816 / EMV, PINpad and More |

| 73S1215F-44IM/F | 功能描述:8位微控制器 -MCU 80515 SoC w/USB & PINpad RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。