- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384065 > μPD45256163 (NEC Corp.) 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD45256163 |

| 廠商: | NEC Corp. |

| 英文描述: | 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) |

| 中文描述: | 256M位同步DRAM(256M同步動(dòng)態(tài)RAM)的 |

| 文件頁數(shù): | 18/84頁 |

| 文件大小: | 1052K |

| 代理商: | ΜPD45256163 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

18

μ

PD45256441,45256841,45256163

Preliminary Data Sheet

(3/3)

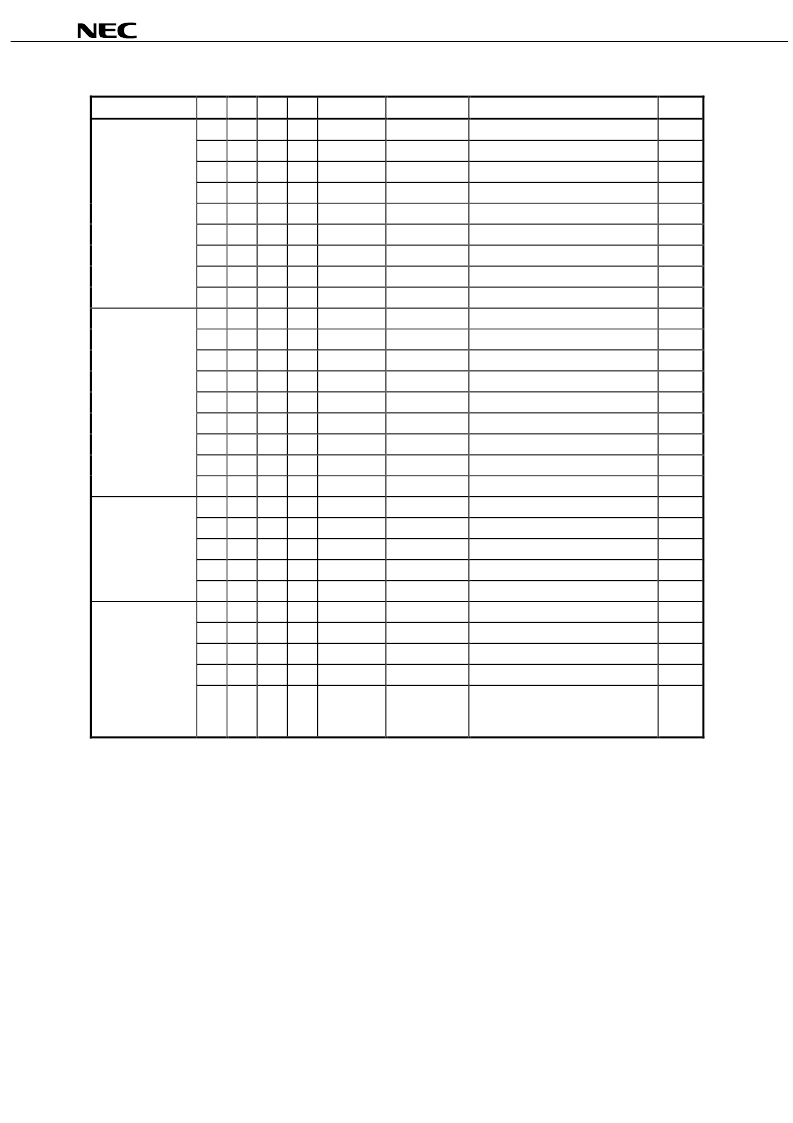

Current state

/CS /RAS /CAS /WE

Address

Command

Action

Notes

Write recovering

H

x

x

x

x

DESL

Nop

→

Enter row active after t

DPL

L

H

H

H

x

NOP

Nop

→

Enter row active after t

DPL

L

H

H

L

x

BST

Nop

→

Enter row active after t

DPL

L

H

L

H

BA, CA, A10 READ/READA

Start read, Determine AP

8

L

H

L

L

BA, CA, A10 WRIT/WRITA

New write, Determine AP

L

L

H

H

BA, RA

ACT

ILLEGAL

3

L

L

H

L

BA, A10

PRE/PALL

ILLEGAL

3

L

L

L

H

x

REF/SELF

ILLEGAL

L

L

L

L

Op-Code

MRS

ILLEGAL

Write recovering

H

x

x

x

x

DESL

Nop

→

Enter precharge after t

DPL

with auto precharge

L

H

H

H

x

NOP

Nop

→

Enter precharge after t

DPL

L

H

H

L

x

BST

Nop

→

Enter precharge after t

DPL

L

H

L

H

BA, CA, A10 READ/READA

ILLEGAL

3, 8

L

H

L

L

BA, CA, A10 WRIT/WRITA

ILLEGAL

3

L

L

H

H

BA, RA

ACT

ILLEGAL

3

L

L

H

L

BA, A10

PRE/PALL

ILLEGAL

L

L

L

H

x

REF/SELF

ILLEGAL

L

L

L

L

Op-Code

MRS

ILLEGAL

Refreshing

H

x

x

x

x

DESL

Nop

→

Enter idle after t

RC

L

H

H

x

x

NOP/BST

Nop

→

Enter idle after t

RC

L

H

L

x

x

READ/WRIT

ILLEGAL

L

L

H

x

x

ACT/PRE/PALL ILLEGAL

L

L

L

x

x

REF/SELF/MRS ILLEGAL

Mode register

H

x

x

x

x

DESL

Nop

→

Enter idle after t

RSC

accessing

L

H

H

H

x

NOP

Nop

→

Enter idle after t

RSC

L

H

H

L

x

BST

ILLEGAL

L

H

L

x

x

READ/WRIT

ILLEGAL

L

L

x

x

x

ACT/PRE/PALL

/REF/SELF/MR

S

ILLEGAL

Notes 1

All entries assume that CKE was active (High level) during the preceding clock cycle.

2.

If all banks are idle, and CKE is inactive (Low level),

μ

PD45256xxx will enter Power down mode.

All input buffers except CKE will be disabled.

3.

Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA),

depending on the state of that bank.

4.

If all banks are idle, and CKE is inactive (Low level),

μ

PD45256xxx will enter Self refresh mode. All

input buffers except CKE will be disabled.

5.

Illegal if t

RCD

is not satisfied.

6.

Illegal if t

RAS

is not satisfied.

7.

Must satisfy burst interrupt condition.

8.

Must satisfy bus contention, bus turn around, and/or write recovery requirements.

9.

Must mask preceding data which don't satisfy t

DPL

.

10.

Illegal if t

RRD

is not satisfied.

Remark

H = High level, L = Low level, x = High or Low level (Don’ t care), V = Valid Data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD45256441 | 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) |

| μPD45256841 | 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) |

| μPD4564163 | 64M-bit Synchronous DRAM(64M同步動(dòng)態(tài)RAM) |

| μPD4564441 | 64M-bit Synchronous DRAM(64M同步動(dòng)態(tài)RAM) |

| μPD4564841 | 64M-bit Synchronous DRAM(64M同步動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD4558C | 制造商:Panasonic Industrial Company 功能描述:IC |

| PD-45A | 功能描述:線性和開關(guān)式電源 40W 5V/3.2A 12V/2A RoHS:否 制造商:TDK-Lambda 產(chǎn)品:Switching Supplies 開放式框架/封閉式:Enclosed 輸出功率額定值:800 W 輸入電壓:85 VAC to 265 VAC 輸出端數(shù)量:1 輸出電壓(通道 1):20 V 輸出電流(通道 1):40 A 商用/醫(yī)用: 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風(fēng)格:Rack 長度: 寬度: 高度: |

| PD-45B | 功能描述:線性和開關(guān)式電源 44.8W 5V/3.2A 24V/1.2A RoHS:否 制造商:TDK-Lambda 產(chǎn)品:Switching Supplies 開放式框架/封閉式:Enclosed 輸出功率額定值:800 W 輸入電壓:85 VAC to 265 VAC 輸出端數(shù)量:1 輸出電壓(通道 1):20 V 輸出電流(通道 1):40 A 商用/醫(yī)用: 輸出電壓(通道 2): 輸出電流(通道 2): 安裝風(fēng)格:Rack 長度: 寬度: 高度: |

| PD45VN6C100 | 制造商:Banner Engineering 功能描述:SENSOR, PHOTOELECTRIC, PICODOT, CONVERGENT LASER, FOCAL POINT, 1 |

| PD45VN6C100Q | 制造商:Banner Engineering 功能描述:Sensor, PicoDot, Convergent Laser, Focal Point: 102mm, Input 10-30VDC, Cable 2m |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。