- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384065 > μPD4265165 (NEC Corp.) 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) PDF資料下載

參數(shù)資料

| 型號: | μPD4265165 |

| 廠商: | NEC Corp. |

| 英文描述: | 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) |

| 中文描述: | 64 m位動態(tài)隨機(jī)存儲器(6400動態(tài)存儲器) |

| 文件頁數(shù): | 9/48頁 |

| 文件大小: | 535K |

| 代理商: | ΜPD4265165 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

μ

PD42S65165, 4265165

9

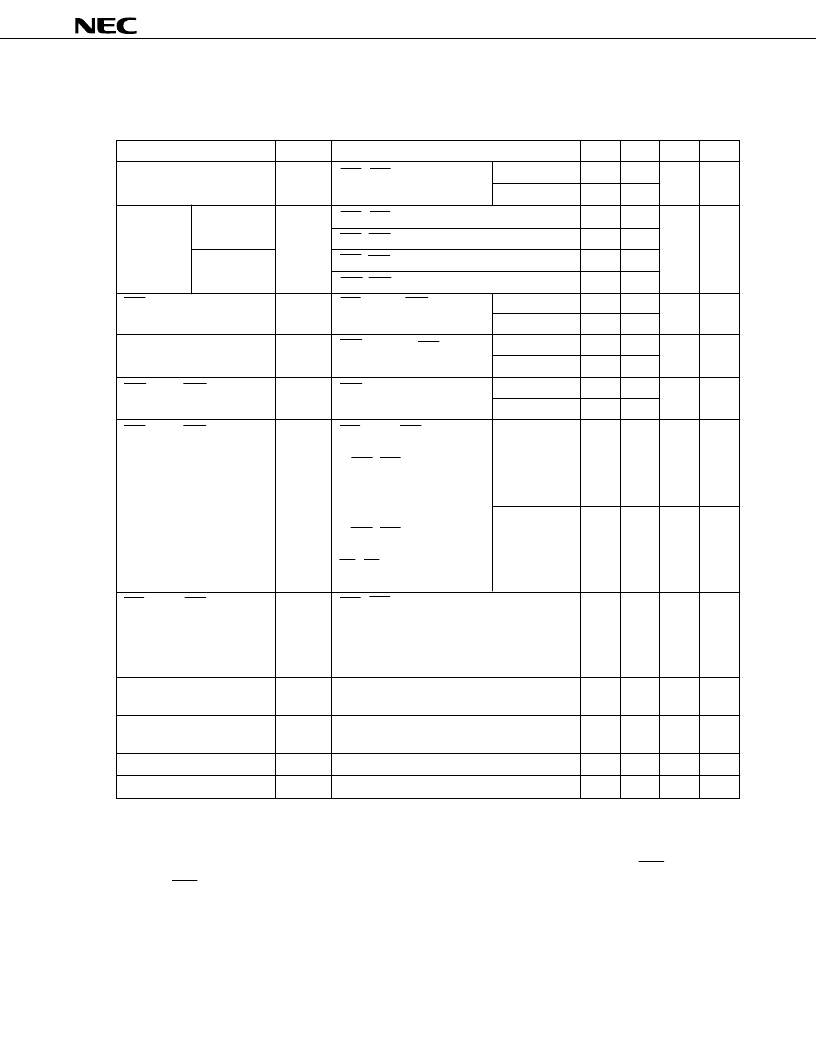

DC Characteristics (Recommended operating conditions unless otherwise noted)

[

μ

PD42S65165, 4265165]

Parameter

Symbol

Test condition

MIN.

MAX.

Unit

Notes

Operating current

I

CC1

RAS, CAS cycling

t

RAC

= 50 ns

150

mA

1, 2, 3

t

RC

= t

RC (MIN.)

, I

O

= 0 mA

t

RAC

= 60 ns

130

Standby

current

μ

PD42S65165

I

CC2

RAS, CAS

≥

V

IH (MIN.)

, I

O

= 0 mA

1.0

mA

RAS, CAS

≥

V

CC

– 0.2 V, I

O

= 0 mA

0.2

μ

PD4265165

RAS, CAS

≥

V

IH (MIN.)

, I

O

= 0 mA

1.0

RAS, CAS

≥

V

CC

– 0.2 V, I

O

= 0 mA

0.5

RAS only refresh current

I

CC3

RAS cycling, CAS

≥

V

IH (MIN.)

t

RC

= t

RC (MIN.)

, I

O

= 0 mA

t

RAC

= 50 ns

150

mA

1, 2, 3 ,4

t

RAC

= 60 ns

130

Operating current

(Hyper page mode (EDO))

I

CC4

RAS

≤

V

IL (MAX.)

, CAS cycling

t

HPC

= t

HPC (MIN.)

, I

O

= 0 mA

t

RAC

= 50 ns

120

mA

1, 2, 5

t

RAC

= 60 ns

100

CAS before RAS

refresh current

I

CC5

RAS cycling

t

RC

= t

RC (MIN.)

, I

O

= 0 mA

t

RAC

= 50 ns

150

mA

1, 2

t

RAC

= 60 ns

130

CAS before RAS

long refresh current

(4,096 cycles/128 ms,

only for the

μ

PD42S65165)

I

CC6

CAS before RAS refresh:

t

RC

= 31.3

μ

s

RAS, CAS:

V

CC

– 0.2 V

≤

V

IH

≤

V

IH (MAX.)

0 V

≤

V

IL

≤

0.2 V

t

RAS

≤

300 ns

500

μ

A

1, 2

Standby:

RAS, CAS

≥

V

CC

– 0.2 V

Address: V

IH

or V

IL

WE, OE: V

IH

I

O

= 0 mA

t

RAS

≤

1

μ

s

600

μ

A

1, 2

CAS before RAS

self refresh current

(only for the

μ

PD42S65165)

I

CC7

RAS, CAS:

t

RASS

= 5 ms

V

CC

– 0.2 V

≤

V

IH

≤

V

IH (MAX.)

0 V

≤

V

IL

≤

0.2 V

I

O

= 0 mA

400

μ

A

2

Input leakage current

I

I (L)

V

I

= 0 to 3.6 V

All other pins not under test = 0 V

–5

+5

μ

A

Output leakage current

I

O (L)

V

O

= 0 to 3.6 V

Output is disabled (Hi-Z)

–5

+5

μ

A

High level output voltage

V

OH

I

O

= –2.0 mA

2.4

V

Low level output voltage

V

OL

I

O

= +2.0 mA

0.4

V

Notes 1.

I

CC1

, I

CC3

, I

CC4

, I

CC5

and I

CC6

depend on cycle rates (t

RC

and t

HPC

).

2.

Specified values are obtained with outputs unloaded.

3.

I

CC1

and I

CC3

are measured assuming that address can be changed once or less during RAS

≤

V

IL (MAX.)

and

CAS

≥

V

IH (MIN.)

.

4.

I

CC3

is measured assuming that all column address inputs are held at either high or low.

5.

I

CC4

is measured assuming that all column address inputs are switched only once during each Hyper page

(EDO) cycle.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD42S65165 | 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) |

| μPD42S17805 | 16M- bit CMOS dynamic RAMs(16M CMOS 動態(tài)RAM) |

| μPD4217805 | 16 M BIT DYNAMIC RAM 2 M WORD BY 8 BIT,EDO |

| μPD42S65405 | 16,777,216 Words by 4 Bits CMOS Dynamic RAMs(64M 動態(tài)RAM) |

| μPD4264405 | 16,777,216 Words by 4 Bits CMOS Dynamic RAMs(64M 動態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD42-CAMG13 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMO12 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMR21 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMR24 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMY01 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。