- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384065 > μPD4265165 (NEC Corp.) 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) PDF資料下載

參數(shù)資料

| 型號: | μPD4265165 |

| 廠商: | NEC Corp. |

| 英文描述: | 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) |

| 中文描述: | 64 m位動態(tài)隨機存儲器(6400動態(tài)存儲器) |

| 文件頁數(shù): | 34/48頁 |

| 文件大?。?/td> | 535K |

| 代理商: | ΜPD4265165 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

μ

PD42S65165, 4265165

34

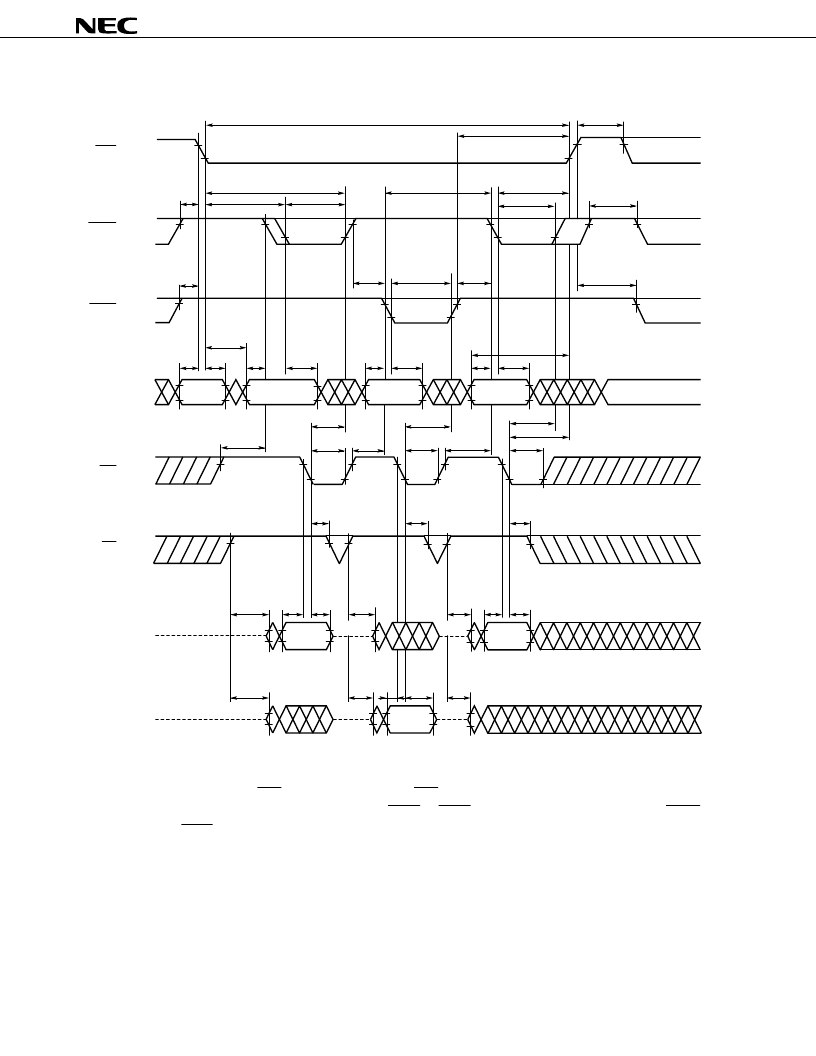

Hyper Page Mode (EDO) Byte Late Write Cycle

RAS

V

IH–

V

IL–

t

RASP

UCAS

V

IH–

V

IL–

U I/O

Hi - Z

V

IH–

V

IL–

t

RP

t

RHCP

t

RSH

t

HCAS

t

HPC

t

CSH

t

RCD

t

CRP

t

HCAS

t

CPN

LCAS

V

IH–

V

IL–

t

CRP

t

MRH

t

CP

t

HCAS

t

CP

Address

V

IH–

V

IL–

OE

V

IH–

V

IL–

L I/O

V

IH–

V

IL–

Data in

t

OED

Hi - Z

Hi - Z

t

DH

Hi - Z

Data in

t

OED

t

OED

Hi - Z

Hi - Z

Data in

t

OED

t

DS

t

OED

t

DS

t

DH

t

OED

t

DS

t

DH

t

OEH

t

OEH

t

OEH

t

WP

t

RCS

t

CWL

t

CWL

t

RCS

t

WP

Row

Col.

Col.

Col.

t

RWL

t

CWL

t

WP

t

RCS

t

RAL

t

CAH

t

ASC

t

CAH

t

ASC

t

CAH

t

ASC

t

RAH

t

ASR

t

RAD

WE

V

IH–

V

IL–

Remarks 1.

In the hyper page mode (EDO), read, write and read modify write cycles are available for each of

the consecutive CAS cycles within the same RAS cycle.

2.

This cycle can be used to control either UCAS or LCAS only. Or, it can be used to control UCAS

or LCAS simultaneously, or at random.

相關PDF資料 |

PDF描述 |

|---|---|

| μPD42S65165 | 64 M-Bit Dynamic Ram(64M 動態(tài)存儲器) |

| μPD42S17805 | 16M- bit CMOS dynamic RAMs(16M CMOS 動態(tài)RAM) |

| μPD4217805 | 16 M BIT DYNAMIC RAM 2 M WORD BY 8 BIT,EDO |

| μPD42S65405 | 16,777,216 Words by 4 Bits CMOS Dynamic RAMs(64M 動態(tài)RAM) |

| μPD4264405 | 16,777,216 Words by 4 Bits CMOS Dynamic RAMs(64M 動態(tài)RAM) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PD42-CAMG13 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMO12 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMR21 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMR24 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

| PD42-CAMY01 | 制造商:P-TEC 制造商全稱:P-tec Corporation 功能描述:Three Digit 7 Segment 0.56” Display |

發(fā)布緊急采購,3分鐘左右您將得到回復。