- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378745 > UPD72042BGT (NEC Corp.) LSI DEVICES FOR Inter Equipment BusTM (IEBusTM) PROTOCOL CONTROL PDF資料下載

參數(shù)資料

| 型號(hào): | UPD72042BGT |

| 廠商: | NEC Corp. |

| 英文描述: | LSI DEVICES FOR Inter Equipment BusTM (IEBusTM) PROTOCOL CONTROL |

| 中文描述: | LSI器件間設(shè)備BusTM(IEBusTM)協(xié)議控制 |

| 文件頁(yè)數(shù): | 32/92頁(yè) |

| 文件大小: | 541K |

| 代理商: | UPD72042BGT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

μ

PD72042A, 72042B

32

DATA SHEET S13990EJ2V0DS00

Address

Name

High-order 4 bits

Low-order 4 bits

Note

Reference page

0H

0000

CTR

–

–

–

REEN SRST

–

–

STREQ

A

p. 33

1H

0001

CMR

0

LOCK

BUFC

COMC

C

p. 34

1

0

0

0

0

IRS

MFC

DERC

2H

0010

UAR1

Local station address

(low-order 4 bits)

Condition code

B

p. 36

3H

0011

UAR2

Local station address (high-order 8 bits)

B

p. 36

4H

0100

SAR1

Slave address

(low-order 4 bits)

0

0

0

0

D

p. 37

5H

0101

SAR2

Slave address (high-order 8 bits)

D

p. 37

6H

0110

MCR

Broadcast bits

Number of

arbitrations

Control bits

D

p. 38

7H

0111

–

–

–

–

8H

1000

–

–

–

–

EH

1110

TBF

Number of bytes of transmission data, transmission data

F

p. 40

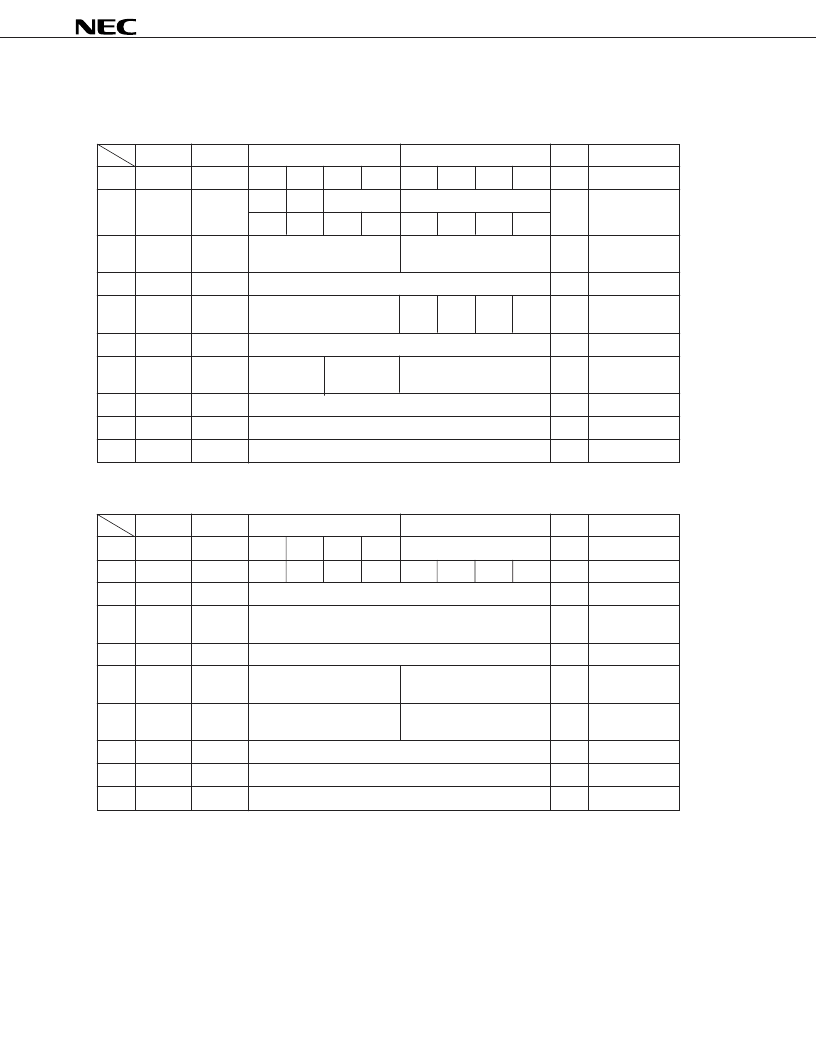

Table 4-1

μ

PD72042A and

μ

PD72042B Registers

(a) Write registers

(b) Read registers

Address

Name

High-order 4 bits

Low-order 4 bits

Note

Reference page

0H

0000

STR

TFL

TEP

RFL

REP

–

A

p. 41

1H

0001

FLG

–

MARQ STRQ SLRE

CEX

RAW

STM

IRQ

A

p. 42

2H

0010

RDR1

Number of bytes of master reception data

A

p. 44

3H

0011

RDR2

Number of bytes of slave reception data or

broadcast reception data

A

p. 44

4H

0100

LOR1

Lock address (low-order 8 bits)

H

p. 45

5H

0101

LOR2

Lock state

Lock address

(high-order 4 bits)

H

p. 45

6H

0110

DAR1

Broadcast address

(low-order 4 bits)

–

E

p. 46

7H

0111

DAR2

Broadcast address (high-order 8 bits)

E

p. 46

8H

1000

RCR

Return codes (MARC, SLRC)

A

p. 47

EH

1110

RBF

Transmitter address, reception data

G

p. 59

Note

Writable and readable periods of the registers of the

μ

PD72042A and

μ

PD72042B

A: Arbitrary

B: After system reset cancellation

C: While CEX of the FLG register (address 0001) is set to 0

D: While MARQ of the FLG register (address 0001) is set to 0

E: After SLRC of the RCR register (address 1000) is set to 1100 (broadcast reception error)

F: While TFL of the STR register (address 0000) is set to 0

G: While REP of the STR register (address 0000) is set to 0

H: When CEX of the FLG register (address 0001) is set to 0 after LOCK of the CMR register (address 0001)

is set to 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD72042A | LSI DEVICES FOR Inter Equipment BusTM (IEBusTM) PROTOCOL CONTROL |

| UPD72042AGT | LSI DEVICES FOR Inter Equipment BusTM (IEBusTM) PROTOCOL CONTROL |

| UPD72042B | LSI DEVICES FOR Inter Equipment BusTM (IEBusTM) PROTOCOL CONTROL |

| UPD72065GC | Floppy Disk Controller |

| UPD72065BGC-3B6 | RTS Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 24V; Output Voltage (Vdc): 15V; Power: 2W; Assembly; High Power Density; Optional Continuous Short Circuit Protected; Efficiency to 85% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD72042BGT-A | 制造商:Renesas Electronics 功能描述:LSI Device 16-Pin SOP 制造商:Renesas Electronics 功能描述:LSI Device 16-Pin SOP Cut Tape |

| UPD72042GT(A) | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD720902AF5-667-JF2-E3-A | 功能描述:IC ADVANCED MEMORY BUFFER D1 RoHS:是 類(lèi)別:集成電路 (IC) >> 接口 - 專(zhuān)用 系列:* 標(biāo)準(zhǔn)包裝:90 系列:- 應(yīng)用:PCI 至 PCI 橋 接口:PCI 電源電壓:3 V ~ 3.6 V 封裝/外殼:257-LFBGA 供應(yīng)商設(shè)備封裝:257-BGA MICROSTAR(16x16) 包裝:托盤(pán) 安裝類(lèi)型:表面貼裝 產(chǎn)品目錄頁(yè)面:882 (CN2011-ZH PDF) 其它名稱(chēng):296-19316 |

| UPD72255YF1-GA5-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7225G | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。