- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383980 > UPD16878GS-BGG (NEC Corp.) MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT PDF資料下載

參數(shù)資料

| 型號: | UPD16878GS-BGG |

| 廠商: | NEC Corp. |

| 英文描述: | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| 中文描述: | 單片四H橋驅(qū)動電路 |

| 文件頁數(shù): | 24/32頁 |

| 文件大?。?/td> | 242K |

| 代理商: | UPD16878GS-BGG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

Data Sheet S15974EJ1V0DS

24

μ

PD16878

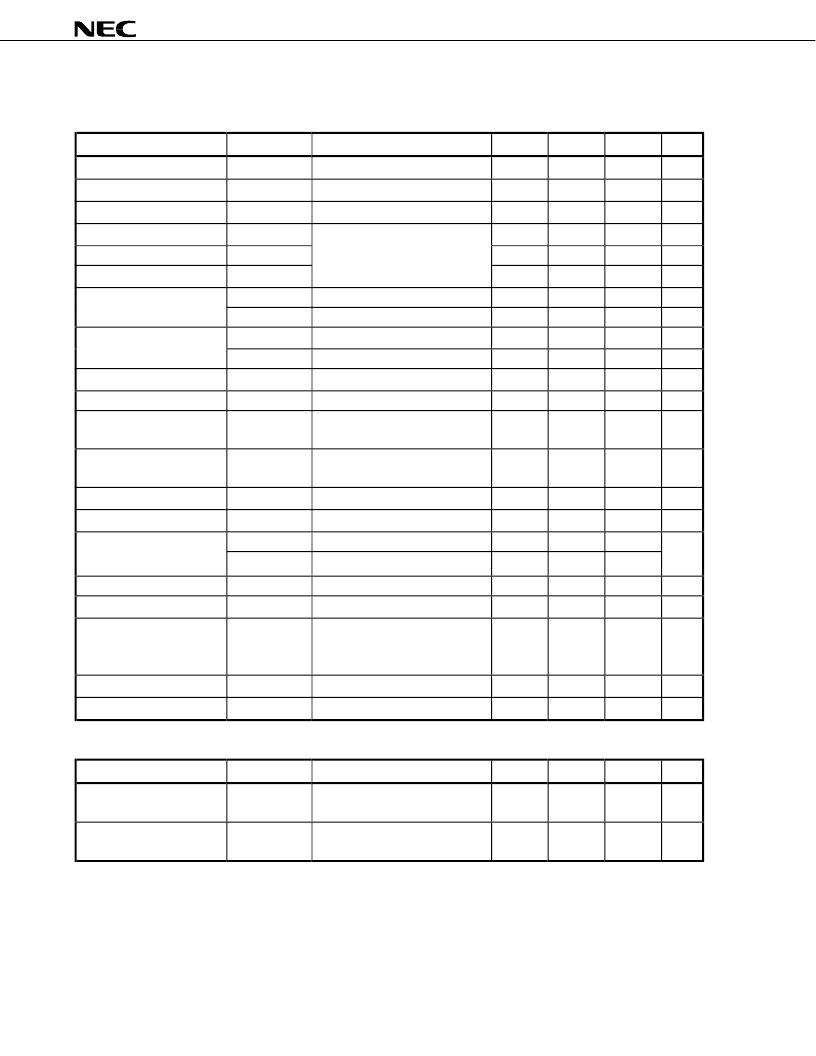

ELECTRICAL CHARACTERISTICS

DC Characteristics (Unless otherwise specified, V

DD

= 3.3 V, V

M

= 6.0 V, V

REF

= 250 mV, T

A

= 25

°

C, f

CLK

= 4 MHz,

C

OSC

= 33 pF, C

FIL

= 1000 pF, EVR = 100 mV (0000))

Parameter

Symbol

Condition

MIN.

TYP.

MAX.

Unit

Off V

M

pin current

I

MO(RESET)

No load, reset period

1.0

μ

A

V

DD

pin current

I

DD

Output open

3.0

mA

V

DD

pin current

I

DD(RESET)

Reset period

100

A

High level input voltage

V

IH

0.7 V

DD

V

Low level input voltage

V

IL

0.3 V

DD

V

Input hysteresis voltage

V

H

LATCH, SCLK, SDATA, V

D

,

RESET, OSC

IN

300

mV

V

OM

α

(H)

, V

OM

β

(H)

5th byte

0.9 V

DD

V

Monitor output voltage 1

(EXT

α

,

β

)

V

OM

α

(L)

, V

OM

β

(L)

5th byte

0.1 V

DD

V

V

OEXP(H)

Pull up (V

DD

)

V

DD

V

Monitor output voltage 2

(EXP0 to EXP3 : open drain)

V

OEXP(L)

I

OEXP

= 100

μ

A

0.1 V

DD

V

High level input current

I

IH

V

IN

= V

DD

0.06

mA

Low level input current

I

IL

V

IN

= 0 V

1.0

μ

A

Reset pin high level input

current

I

IH(RST)

V

RST

= V

DD

1.0

μ

A

Reset pin low level input

current

I

IL(RST)

V

RST

= 0

1.0

μ

A

Input pull down resistor

R

IND

LATCH, SCLK, SDATA, V

D

50

200

k

H bridge ON resistance

Note 1

R

ON

I

M

= 100 mA

3.5

5.0

f

OSC(1)

DATA: 00000 (4th byte)

0

Chopping frequency (internal

oscillation: C

OSC

= 100 pF)

f

OSC(2)

DATA: 11111 (4th byte)

100

124

150

kHz

Step frequency

f

STEP

Minimum step

4

kHz

V

D

delay time

Note 2

t

VD

250

ns

Sine wave peak output

current

Note 3

I

M

L = 25 mH/R = 100

(1 kHz)

EVR = 200 mV (1010)

R

S

= 6.8

, f

OSC

= 64 kHz

52

mA

FIL pin voltage

Note 4

V

EVR

EVR = 200 mV (1010)

370

400

430

mV

FIL pin step voltage

Note 4

V

EVRSTEP

Minimum step

20

mV

AC Characteristics (Unless otherwise specified, V

DD

= 3.3 V, V

M

= 6.0 V, T

A

= 25

°

C, f

CLK

= 4 MHz)

Parameter

Symbol

Condition

MIN.

TYP.

MAX.

Unit

H bridge output circuit turn on

time

t

ONH

I

M

= 100 mA

Note 5

1.0

2.0

μ

s

H bridge output circuit turn off

time

t

OFFH

I

M

= 100 mA

Note 5

1.0

2.0

μ

s

Notes 1.

Total of ON resistance at top and bottom of output H bridge

2.

By OSC

IN

and V

D

sync circuit

3.

FB pin is monitored.

4.

FIL pin is monitored. A voltage about twice that of the EVR value is output to the FIL pin.

5.

10 to 90% of the pulse peak value without filter capacitor (C

FIL

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD16878 | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879GS-BGG | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879 | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD1703C-011 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

| UPD1703C-013 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD16879 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879GS-BGG | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16882 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16882GS | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16886 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC 1.5-CHANNEL H BRIDGE DRIVER CIRCUIT FOR CAMERAS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。