- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383980 > UPD16878GS-BGG (NEC Corp.) MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT PDF資料下載

參數(shù)資料

| 型號: | UPD16878GS-BGG |

| 廠商: | NEC Corp. |

| 英文描述: | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| 中文描述: | 單片四H橋驅(qū)動電路 |

| 文件頁數(shù): | 18/32頁 |

| 文件大?。?/td> | 242K |

| 代理商: | UPD16878GS-BGG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

Data Sheet S15974EJ1V0DS

18

μ

PD16878

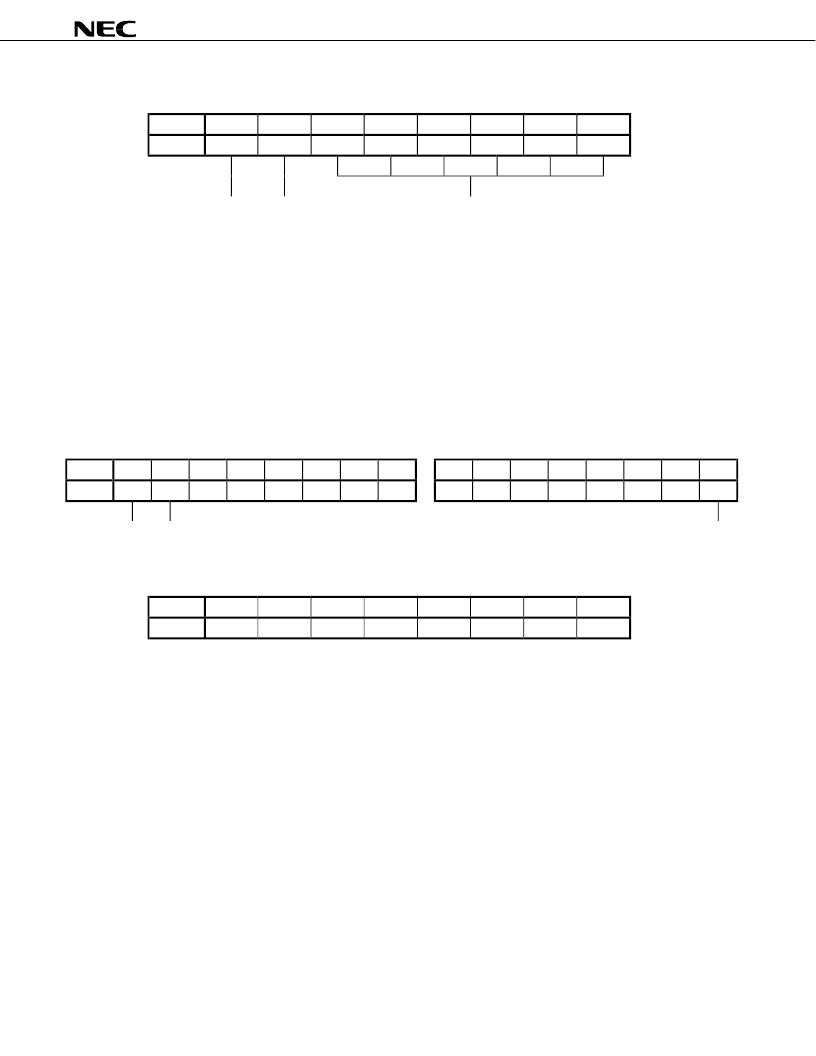

Table 5-11. 5th Byte Data Configuration (Standard data)

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Data

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

Rotation direction ENABLE Number of pulses

<6th and 7th bytes>

The 6th and 7th bytes select the pulse cycle of the

β

channel and which of the two reference voltages, created in

the initial mode, is to be used (CURRENT SET

β

).

The pulse cycle is specified using 15 bits : bits D0 (least significant bit) to D7 of the 6th byte, and bits D0 to D6

(most significant bit) of the 7th byte. The pulse cycle can be set to a value in the range of 0.25 to 8191.75

μ

s in units

of 0.25

μ

s (with a 4-MHz clock).

CURRENT SET

β

is specified by bit D7 of the 7th byte. When this bit is

“

0

”

, reference voltage 1 (EVR

β

1

) is

selected; when it is

“

1

”

, reference voltage 2 (EVR

β

2

) is selected. For further information, refer to the description of the

7th byte of the initial data.

Table 5-12. 7th Byte Data Configuration (Standard data)

Table 5-13. 6th Byte Data Configuration (Standard data)

Bit

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

Data

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

CURRENT SET

β

Most significant bit

Least significant bit

(Reference) 7th Byte Data Configuration for Initial Data

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Data

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

Remark

Bits D4 to D7 : Reference voltage 2 (EVR

β

2

)

Bits D0 to D3 : Reference voltage 1 (EVR

β

1

)

<8th byte>

The 8th byte is checksum data. Normally, the sum of the 8-byte data is 00H.

If the sum is not 00H because data transmission is abnormal, the stepping operation is inhibited and the

checksum output pin (EXT pin) is held at

“

L

”

.

相關PDF資料 |

PDF描述 |

|---|---|

| UPD16878 | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879GS-BGG | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879 | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD1703C-011 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

| UPD1703C-013 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD16879 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16879GS-BGG | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16882 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16882GS | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16886 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC 1.5-CHANNEL H BRIDGE DRIVER CIRCUIT FOR CAMERAS |

發(fā)布緊急采購,3分鐘左右您將得到回復。