- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC22X5YA (Fairchild Semiconductor Corporation) Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit PDF資料下載

參數(shù)資料

| 型號: | TMC22X5YA |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| 中文描述: | 多標(biāo)準(zhǔn)數(shù)字視頻解碼器三線自適應(yīng)梳狀解碼器系列,8 |

| 文件頁數(shù): | 36/84頁 |

| 文件大?。?/td> | 417K |

| 代理商: | TMC22X5YA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

TMC22x5yA

PRODUCT SPECIFICATION

36

REV. 1.0.0 2/4/03

Control Register De

fi

nitions

(continued)

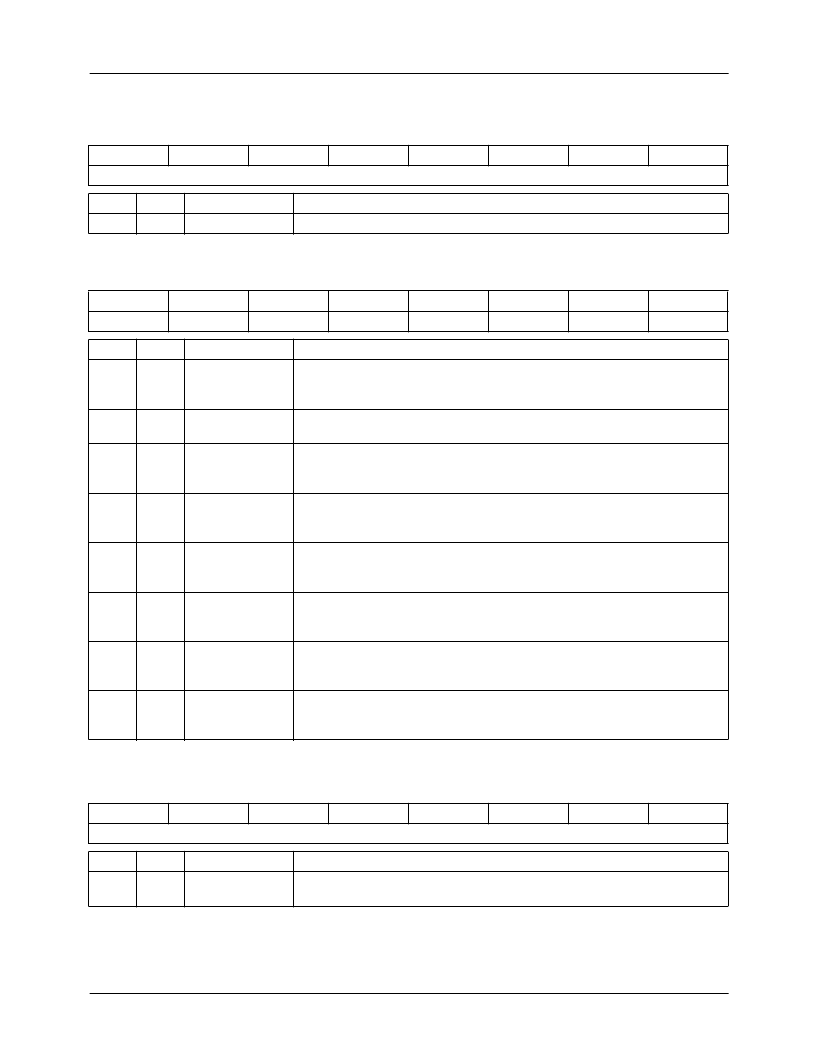

Test Control (3D-3E)

7

6

5

4

3

2

1

0

TEST

Reg

3D-3E

Bit

7-0

Name

TEST

Description

Must be set to zero.

Auto increment stops at 3F

Test Control (3F)

7

6

5

4

3

2

1

0

VBIT20

PEDDIS

CCDEN

5

CCDEN

4

CCDEN

3

CCDEN

2

CCDEN

1

CCDEN

0

Reg

3F

Bit

7

Name

VBIT20

Description

VBIT20 enable.

When HIGH the V bit within embedded TRS words is

extended through line 20 for NTSC. When LOW, this V bit is HIGH up to line

16 for NTSC. The PAL operation is unaffected by this register bit.

Pedestal disable.

When HIGH, pedestal is not removed from lines with

LID = 00 to 06, lines 0 through 16

Closed caption data enable 5.

When HIGH, enables NTSC line 21 field 0

or PAL line 22 field 0 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

Closed caption data enable 4.

When HIGH, enables NTSC line 22 field 0

or PAL line 23 field 0 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

Closed caption data enable 3.

When HIGH, enables NTSC line 23 field 0

or PAL line 24 field 0 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

Closed caption data enable 2.

When HIGH, enables NTSC line 283 field 1

or PAL line 334 field 1 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

Closed caption data enable 1.

When HIGH, enables NTSC line 284 field 1

or PAL line 335 field 1 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

Closed caption data enable 0.

When HIGH, enables NTSC line 285 field 1

or PAL line 336 field 1 to be passed ‘FLAT’, through the decoder, on the

luminance channel and the pedestal removal will be disabled.

3F

6

PEDDIS

3F

5

CCDEN

5

3F

4

CCDEN

4

3F

3

CCDEN

3

3F

2

CCDEN

2

3F

1

CCDEN

1

3F

0

CCDEN

0

Status - Read Only (40)

7

6

5

4

3

2

1

0

DDSPH

Reg

40

Bit

7-0

Name

DDSPH

Description

DDS phase, 8 msbs.

The top 8 bits of the sine data generated in the internal

DDS.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC22052AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22053AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22151AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22152AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22153AKHC | JT 32C 32#20 SKT PLUG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC2302A | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Image Manipulation Sequencer |

| TMC2302AH5C | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC2302AH5C1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC2302AKEC | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Image Manipulation Sequencer |

| TMC2302AKEC1 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Image Manipulation Sequencer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。