- 您現在的位置:買賣IC網 > PDF目錄384004 > TLC320AD57C (Texas Instruments, Inc.) Sigma-Delta Stereo Analog-to-Digital Converter PDF資料下載

參數資料

| 型號: | TLC320AD57C |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Sigma-Delta Stereo Analog-to-Digital Converter |

| 中文描述: | Σ-Δ立體聲模擬數字轉換器 |

| 文件頁數: | 12/21頁 |

| 文件大小: | 133K |

| 代理商: | TLC320AD57C |

2–4

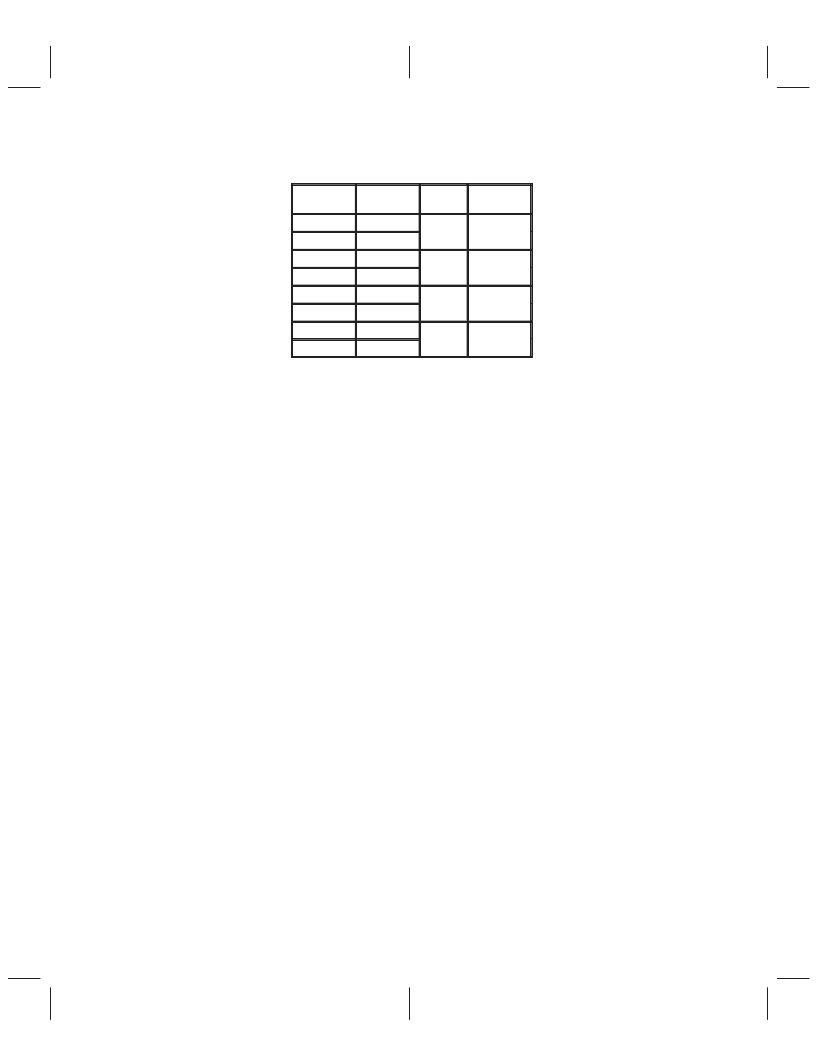

Table 2–1. Master-Clock to Sample-Rate Comparison

(modes 1, 3, 4, 5)

MCLK

(MHz)

CMODE

SCLK

(MHz)

LRClk

(kHz)

12.2880

Low

3 0720

3.0720

48

18.4320

High

11.2896

Low

2 8224

2.8224

44 1

44.1

16.9344

High

8.1920

Low

2 0480

2.0480

32

12.2880

High

0.2560

0.3840

Low

High

0 0640

0.0640

1

2.7

When the TEST input is high, the test mode is selected, which routes the high speed one-bit modulator result

to the serial port output. When in the test mode, the SCLK output frequency is equal to the data output rate.

LRClk is an input when the test mode is selected. This allows for the selection of the left or right modulator

output to be routed to the serial port (high = left and low = right).

Test

2.8

Although the serial data is shifted out in two seperate time packets that represent the left and right channels,

the inputs are sampled and converted simultaneously.

Serial Interface

The serial interface protocol has master and slave modes each with different read-out modes. The master

mode sources the control signals for conversion synchronization while the slave mode allows an external

controller to provide conversion synchronization signals.

The five master modes are shown in Figures 2–3(a) through 2–3(e) and the three slave modes are shown

in Figures 2–4(a) through 2–4(c). For a 16-bit word, D15 is the most significant bit and D0 is the least

significant bit. Unless otherwise specified, all values are in 2s complement format.

In the master mode, SCLK is generated internally and is sourced as an output. The relationship of SCLK

to LRClk is 64

×

(modes 1, 3, 4, 5) or 32

×

(modes 6, 7). In the slave mode, SCLK is an input. SCLK timing

must meet the timing specifications listed in the Recommended Operating Conditions section.

2.8.1

As the master, the TLC320AD57C generates LRClk, Fsync, and SCLK from MCLK. These signals are

provided for synchronizing the serial port of a DSP or other control devices.

Master Mode

Fsync designates valid data from the ADC, and accomplishes this in the master modes by one of two

methods. The first method is to place a single pulse on Fsync prior to valid data. This indicates the starting

point for the data. The second method of frame synchronization is to hold Fsync high during the entire valid

data cycle which provides boundaries for the data.

LRClk is generated internally from MCLK. The frequency of this signal is fixed at the sampling frequency

f

s

[MCLK/256 (CMODE low) or MCLK/384 (CMODE high)]. During the high period of this signal, the left

channel data is serially shifted to the output; during the low period, the right channel data is shifted to the

output. The conversion cycle synchronizes with the rising edge of LRClk.

Five modes are available when the device is configured as a master. Two modes are for 18-bit

communications. These modes differ from each other in that the MSB is transferred first in one mode while

the LSB is transferred first in the second mode [see Figures 2–3(b) and 2–3(c)]. When the LSB is transferred

first, the data is right justified to the LRClk [see Figures 2–3(a) through 2–3(e)]. The three other modes

相關PDF資料 |

PDF描述 |

|---|---|

| TLC320AD58(中文) | Sigma-Delta Analog Interface Circuit(Sigma-Delta立體聲音頻ADC) |

| TLC320AD58C | Sigma-Delta Stereo Analog-to-Digital Converter |

| TLC320AD75C | 20-Bit Sigma-Delta Stereo ADA Circuit |

| TLC320AD77C | 24-BIT 96 kHz STEREO AUDIO CODEC |

| TLC320AD80C | Audio Processor Subsystem |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLC320AD57CDW | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

| TLC320AD57CDWR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

| TLC320AD58 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

| TLC320AD58C | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

| TLC320AD58CDW | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Sigma-Delta Stereo Analog-to-Digital Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復。