- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383876 > T7690 (Lineage Power) 5.0 V T1/E1 Quad Line Interface(5.0 V T1/E1 四線接口) PDF資料下載

參數(shù)資料

| 型號: | T7690 |

| 廠商: | Lineage Power |

| 英文描述: | 5.0 V T1/E1 Quad Line Interface(5.0 V T1/E1 四線接口) |

| 中文描述: | 5.0V的四線接口的T1/E1(5.0V的T1/E1的四線接口) |

| 文件頁數(shù): | 35/42頁 |

| 文件大?。?/td> | 726K |

| 代理商: | T7690 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Data Sheet

May 1998

T7690 5.0 V T1/E1 Quad Line Interface

T7693 3.3 V T1/E1 Quad Line Interface

33

Lucent Technologies Inc.

XCLK Reference Clock

The device requires a high-frequency reference clock

for both clock/data recovery and jitter attenuation

options (CDR = 1, JAR = 1, or JAT = 1). The XCLK sig-

nal (pin 29) is conditionally required if the MPCLK sig-

nal (pin 83) is not supplied for interrupt generation in

the microprocessor interface. For any other device con-

figuration, XCLK is not required. If it is required, XCLK

must be a continuously active (i.e., ungapped, unjit-

tered, and unswitched) and an independent reference

clock such as an external system oscillator or system

clock for proper operation. It must not be derived from

any recovered line clock (i.e., from RCLK or any syn-

thesized frequency of RCLK). The specifications for

XCLK are defined in Table 22.

Power Supply Bypassing

External bypassing is required for all channels. A

1.0

μ

F capacitor must be connected between V

DD

X

and GNDX. In addition, a 0.1

μ

F capacitor must be

connected between V

DDD

and GND

D

, and a 0.1

μ

F

capacitor must be connected between V

DDA

and

GND

A

. Ground plane connections are required for

GNDX, GND

D

, and GND

A

. Power plane connections

are also required for V

DD

X and V

DDD

. The need to

reduce high-frequency coupling into the analog supply

(V

DDA

) may require an inductive bead to be inserted

between the power plane and the V

DDA

pin of every

channel.

External bypassing is also required for the micropro-

cessor power supply pins. A 0.1

μ

F capacitor must be

connected between every pair of V

DDC

and GND

C

pins.

V

DDC

and GND

C

are connected directly to the power

and ground planes, respectively.

Capacitors used for power supply bypassing should be

placed as close as possible to the device pins for maxi-

mum effectiveness.

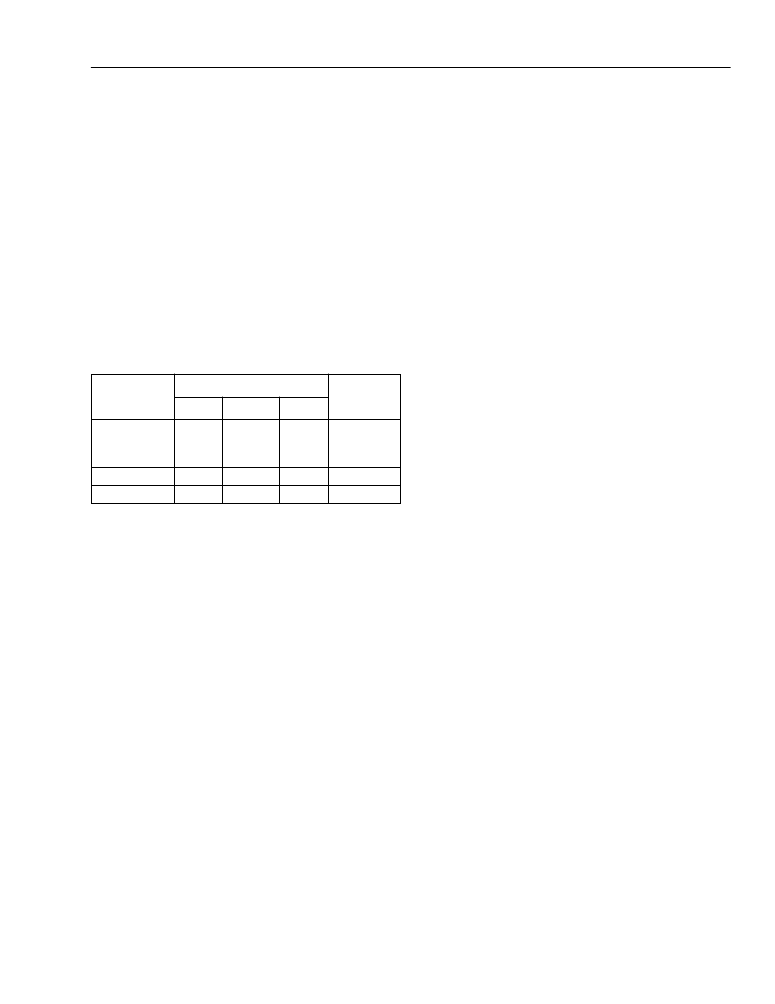

Table 22. XCLK Timing Specifications

Parameter

Value

Unit

Min

Typ

Max

Frequency

DS1

CEPT

Range

Duty Cycle

—

—

24.704

32.768

—

—

—

—

100

60

MHz

MHz

ppm

%

–100

40

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7693 | 3.3 V T1/E1 Quad Line Interface( 3.3 V T1/E四線接口) |

| T7698 | Quad T1/E1 Line Interface and Octal T1/E1 Monitor(四T1/E1線接口和八T1/E1監(jiān)控器) |

| T7705A | SUPPLY-VOLTAGE SUPERVISORS |

| T8100A | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時間段交換機(jī)) |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線時隙交換機(jī)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T-7690-FL | 制造商:Alcatel-Lucent 功能描述:PCM TRANSCEIVER, Quad, CEPT PCM-30/E-1, 100 Pin, Plastic, QFP |

| T77 | 制造商:Thomas & Betts 功能描述:2-1/2"CONDUIT BODY,IRON,T,F-7 制造商:Cooper Crouse-Hinds 功能描述: 制造商:Thomas & Betts 功能描述:Fittings T-Fitting 2.5inch Non-Thread Iron |

| T7700 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Core2 Duo Processors and Core2 Extreme Processors for Platforms Based on Mobile 965 Express Chipset Family |

| T77000150 | 制造商:Assembly Value Added 功能描述: |

| T7705102CA | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。