- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25648 > STM32W108HBU7 (STMICROELECTRONICS) SPECIALTY MICROPROCESSOR CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號: | STM32W108HBU7 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, 0.50 MM PITCH, ROHS COMPLIANT, VFQFPN-40 |

| 文件頁數(shù): | 191/198頁 |

| 文件大?。?/td> | 2871K |

| 代理商: | STM32W108HBU7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁當(dāng)前第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁

Serial interfaces

STM32W108CB, STM32W108HB

Doc ID 16252 Rev 3

9.13.2

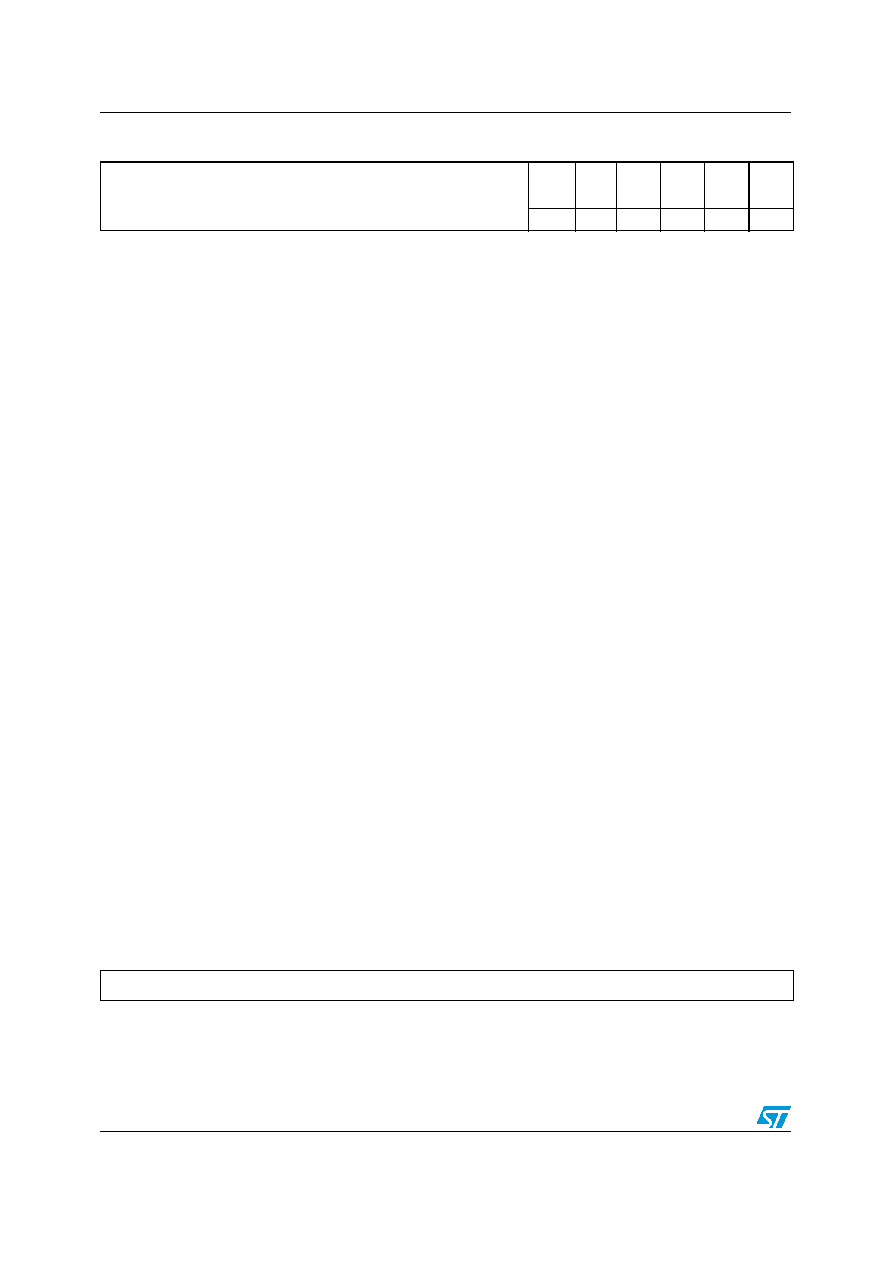

Serial DMA status register (SCx_DMASTAT)

Address offset: 0xC82C (SC1_DMASTAT) and 0xC02C (SC2_DMASTAT)

Reset value:

0x0000 0000

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Reserved

SC_TX

DMARS

T

SC_R

XDMA

RST

SC_TX

LODB

SC_TX

LODA

SC_RX

LODB

SC_RX

LODA

w

rw

Bit 5 SC_TXDMARST: Setting this bit resets the transmit DMA. The bit clears automatically.

Bit 4 SC_RXDMARST: Setting this bit resets the receive DMA. The bit clears automatically.

Bit 3 SC_TXLODB: Setting this bit loads DMA transmit buffer B addresses and allows the DMA

controller to start processing transmit buffer B. If both buffer A and B are loaded simultaneously,

buffer A will be used first. This bit is cleared when DMA completes. Writing a zero to this bit has

no effect.

Reading this bit returns DMA buffer status:

0: DMA processing is complete or idle.

1: DMA processing is active or pending.

Bit 2 SC_TXLODA: Setting this bit loads DMA transmit buffer A addresses and allows the DMA

controller to start processing transmit buffer A. If both buffer A and B are loaded simultaneously,

buffer A will be used first. This bit is cleared when DMA completes. Writing a zero to this bit has

no effect.

Reading this bit returns DMA buffer status:

0: DMA processing is complete or idle.

1: DMA processing is active or pending.

Bit 1 SC_RXLODB: Setting this bit loads DMA receive buffer B addresses and allows the DMA

controller to start processing receive buffer B. If both buffer A and B are loaded simultaneously,

buffer A will be used first. This bit is cleared when DMA completes. Writing a zero to this bit has

no effect.

Reading this bit returns DMA buffer status:

0: DMA processing is complete or idle.

1: DMA processing is active or pending.

Bit 0 SC_RXLODA: Setting this bit loads DMA receive buffer A addresses and allows the DMA

controller to start processing receive buffer A. If both buffer A and B are loaded simultaneously,

buffer A will be used first. This bit is cleared when DMA completes. Writing a zero to this bit has

no effect.

Reading this bit returns DMA buffer status:

0: DMA processing is complete or idle.

1: DMA processing is active or pending.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STP506C-2IW-012V | SINGLE COLOR DISPLAY CLUSTER, WHITE, 152.4 mm |

| SUGR47M | DUAL COLOR LED, RED/GREEN, 5 mm |

| SUR76D | SINGLE COLOR LED, RED, 3 mm |

| SUY17D | SINGLE COLOR LED, YELLOW, 3.9 mm |

| SY405T | SINGLE COLOR LED, AMBER, 2.7 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| STM32WC-RFCKIT | 功能描述:Zigbee/802.15.4開發(fā)工具 STM32W Low-Cost RF STM32F103 MCU Kit RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評估:EM35x 頻率:2.4 GHz 接口類型:USB 工作電源電壓: |

| STM32W-RFCKIT | 功能描述:開發(fā)板和工具包 - 無線 STM32W RF CNTRL KIT STM32F103 USB JTAG RoHS:否 制造商:Arduino 產(chǎn)品:Evaluation Boards 工具用于評估:AT32UC3L 核心:AVR32 頻率: 接口類型:USB 工作電源電壓:5 V |

| STM3-3 | 制造商:RINO MECH.(GENGARELL 功能描述: |

| STM330 | 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 868MHz |

| STM330U | 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 315MHz 制造商:EnOcean GmbH 功能描述:Temperature energy harvester, 902MHz |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。