- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SST55LD040M-133-C-BZJE IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA145 PDF資料下載

參數(shù)資料

| 型號: | SST55LD040M-133-C-BZJE |

| 元件分類: | 存儲控制器/管理單元 |

| 英文描述: | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA145 |

| 封裝: | 12 X 12 MM, 1.07 MM HEIGHT, ROHS COMPLIANT, TFBGA-145 |

| 文件頁數(shù): | 37/39頁 |

| 文件大小: | 589K |

| 代理商: | SST55LD040M-133-C-BZJE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁

Advance Information

NAND Controller

SST55LD040M

2010 Silicon Storage Technology, Inc.

S71408-01-000

04/10

7

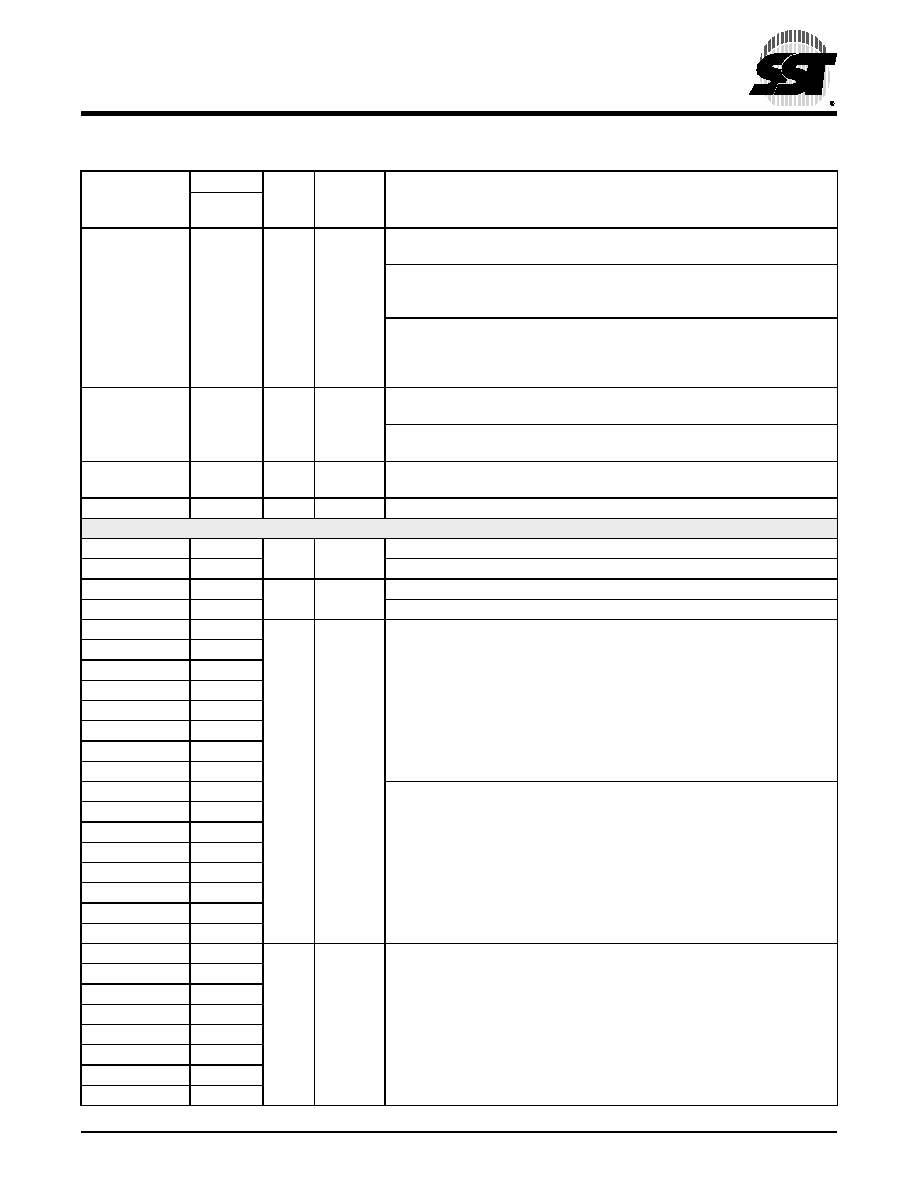

IORD#

H12

I

I2Z

IORD#: This is an I/O Read strobe generated by the host. While Ultra DMA

mode is not active, this signal gates I/O data from the device.

HDMARDY#: In Ultra DMA mode when DMA Read is active, this signal is

asserted by the host to indicate that the host is ready to receive Ultra DMA data-

in bursts. The host may negate HDMARDY# to pause an Ultra DMA transfer.

HSTROBE: When DMA Write is active, this signal is the data-out strobe gen-

erated by the host. Both the rising and falling edges of HSTROBE cause data

to be latched by the device. The host may stop generating HSTROBE edges

to pause an Ultra DMA data-out burst.

IOWR#

G3

I

I2Z

IOWR#: This is an I/O Write strobe generated by the host. When Ultra

DMA is not active, this signal clocks I/O into the device.

STOP: When Ultra DMA mode protocol is active, the assertion of this sig-

nal causes the termination of the Ultra DMA burst.

IOCS16#

G1

O

O3

This output signal is asserted low when the device is indicating a word data

transfer cycle.

PDIAG#

F3

I/O

I1U/O2

The Pass Diagnostic signal in the Master/Slave handshake protocol.

Flash Media Interface1

F0RE#

P7

OO7

Active Low Flash Media Chip Read [MIB0]

F0WE#

N1

Active Low Flash Media Chip Write [MIB0]

F0CLE

N2

OO6

Active High Flash Media Chip Command Latch Enable [MIB0]

F0ALE

P2

Active High Flash Media Chip Address Latch Enable [MIB0]

F0AD15

N8

I/O

I3U/O6

Flash Media Chip High Byte Address/Data Bus pins [MIB0]

F0AD14

M9

F0AD13

P9

F0AD12

N10

F0AD11

N11

F0AD10

P12

F0AD9

N13

F0AD8

M14

F0AD7

P8

Flash Media Chip Low Byte Address/Data Bus pins [MIB0]

F0AD6

N9

F0AD5

M10

F0AD4

P10

F0AD3

P11

F0AD2

M13

F0AD1

P13

F0AD0

N14

F0CE7#

M6

O

O5

Active Low Flash Media Chip Enable pin [MIB0]

F0CE6#

M2

F0CE5#

N6

F0CE4#

P3

F0CE3#

P6

F0CE2#

N3

F0CE1#

N5

F0CE0#

P4

TABLE

1: Pin Assignments (Continued) (2 of 4)

Symbol

Ball No.

Ball

Type

I/O

Type

Name and Functions

145

TFBGA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SST55VD020-60-C-MVWE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA85 |

| SST55VD020-60-I-TQWE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PQFP100 |

| SST55VD020-60-C-MVWE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA85 |

| SST55VD020-60-I-TQWE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PQFP100 |

| SST85LD0512-60-RI-LBTE | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SST55VD020-60-C-MVWE | 功能描述:閃存 ATA Media 60MHz 3.3V Commercial RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結(jié)構(gòu):256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST55VD020-60-C-TQWE | 功能描述:閃存 ATA Media 60MHz 2.7V Commercial RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結(jié)構(gòu):256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST55VD020-60-I-MVWE | 功能描述:總線收發(fā)器 ATA Media 60MHz 3.3V Industrial RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SST55VD020-60-I-TQWE | 功能描述:閃存 ATA Media 60MHz 3.3V Industrial RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結(jié)構(gòu):256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST55VD020-60-I-TQWE-TM024 | 功能描述:閃存 ATA Media 60MHz 3.3V Industrial RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲類型:Flash 存儲容量:2 MB 結(jié)構(gòu):256 K x 8 定時類型: 接口類型:SPI 訪問時間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。