- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374749 > SDA9588X (MICRONAS SEMICONDUCTOR HOLDING AG) Cost-effective Picture-In-Picture ICs PDF資料下載

參數(shù)資料

| 型號: | SDA9588X |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 畫面疊加 |

| 英文描述: | Cost-effective Picture-In-Picture ICs |

| 中文描述: | PICTURE-IN-PICTURE IC, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁數(shù): | 32/87頁 |

| 文件大?。?/td> | 2045K |

| 代理商: | SDA9588X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁

SDA 9488X

SDA 9588X

System Description

Micronas

4-32

Preliminary Data Sheet

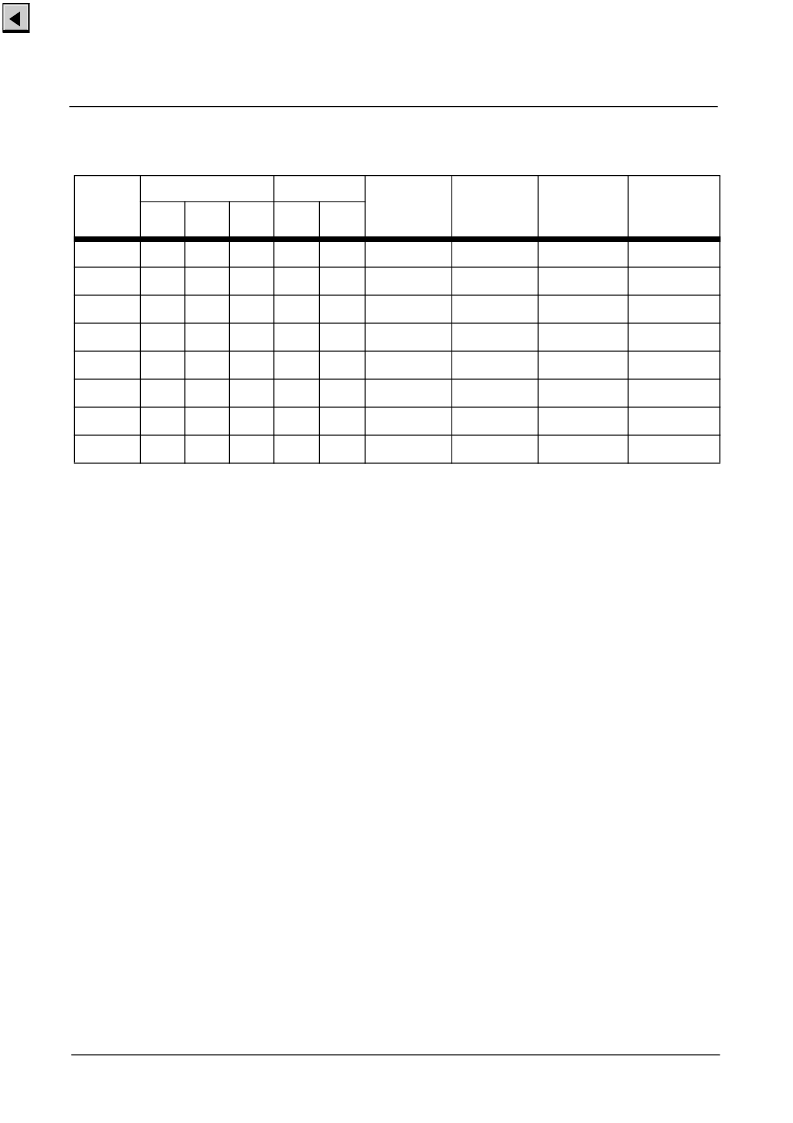

Table 4-18

PIP horizontal blanking timing

4.9.1

The peak level adjustment modifies the magnitude of each channel separately. It should

be used to adapt once the signal levels to the following stage. The contrast adjustment

influences all three channels and allows a further increase of 30% of the peak level

magnitude. The effect of the brightness adjustment depends on the selected output

mode (RGB/YUV). In YUV mode it changes the offset of the OUT2 (Y) signal only while

in RGB mode it changes the offset of all three channels at the same time. The brightness

increase is up to 20%.

Contrast, Brightness and Peak Level Adjustment

4.9.2

The pedestal level adjustment controlled by I

2

C signals

BLKLR

,

BLKLG

,

BLKLB

enables the correction of small offset errors, possibly appearing at the successive

blanking stage of RGB processor. This adjustment has an effect on the setup level

during the active line interval of each channel like the brightness adjustment but has an

enhanced resolution of 0.5 LSB. The maximum possible offset amounts to 7.5 LSBs. In

YUV mode (

OUTFOR

= ’1’) the action depends on the setting of

BLKINVR

and

BLKINVB

. If

BLKINVR

(

BLKINVB

) is active the offset applies to the blank level of the

RV

(

BU

) channel during the clamping interval for shifting the setup level to the negative

direction. In RGB mode (

OUTFOR

= ’0’)

BLKINVR

and

BLKINVB

have no effect.

Pedestal Level Adjustment

READD

CLPDEL

CLPLEN

a (

←

s)

Blanking

Start

b (

←

s)

Blanking

Duration

c (

←

s)

Clamping

Start

d (

←

s)

Clamping

Duration

D2

D1

D0

D1

D0

0

0

0

0

0

0

-1.5

10.5

3

5

0

1

1

1

0

0

-11

10.5

-6.4

5

0

0

0

0

0

1

-1.5

7.9

2.2

3.8

0

1

1

1

0

1

-11.0

7.9

-7.3

3.8

1

0

0

0

0

0

-0.8

5.3

1.5

2.5

1

1

1

1

0

0

-5.5

5.3

-3.2

2.5

1

0

0

0

0

1

-0.8

4

1.1

1.9

1

1

1

1

0

1

-5.5

4

-3.6

1.9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SDA9489X | PIP IV Advanced SOPHISTICUS High-End Picture-In-Picture ICs |

| SDA9589X | PIP IV Advanced SOPHISTICUS High-End Picture-In-Picture ICs |

| SDB14 | 1.0 AMP. Schottky Barrier Rectifiers |

| SDB15 | 1.0 AMP. Schottky Barrier Rectifiers |

| SDB16 | 1.0 AMP. Schottky Barrier Rectifiers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SDA9589X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PIP IV Advanced SOPHISTICUS High-End Picture-In-Picture ICs |

| SDAB-15P | 制造商:HRS 制造商全稱:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

| SDAB-15P(55) | 制造商:Hirose Electric 功能描述:2.74mm 15 2 Zv^N ^Cv 39.14mm 350VAC 3A 5000M/500VDC 15m/100mA 1250VAC/1min. +85 -55 PBT/UL94V-0/ jbPbL+bL AWG#28 to #30 12.55mm Bulk |

| SDAB-15P05 | 制造商:HRS 制造商全稱:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

| SDAB-15S | 制造商:HRS 制造商全稱:HRS 功能描述:STRAIGHT/METAL PCB D-SUB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。