- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382394 > PLL1700E MULTI-CLOCK GENERATOR PDF資料下載

參數(shù)資料

| 型號: | PLL1700E |

| 英文描述: | MULTI-CLOCK GENERATOR |

| 中文描述: | 多時鐘發(fā)生器 |

| 文件頁數(shù): | 5/9頁 |

| 文件大?。?/td> | 137K |

| 代理商: | PLL1700E |

5

PLL1700

THEORY OF OPERATION

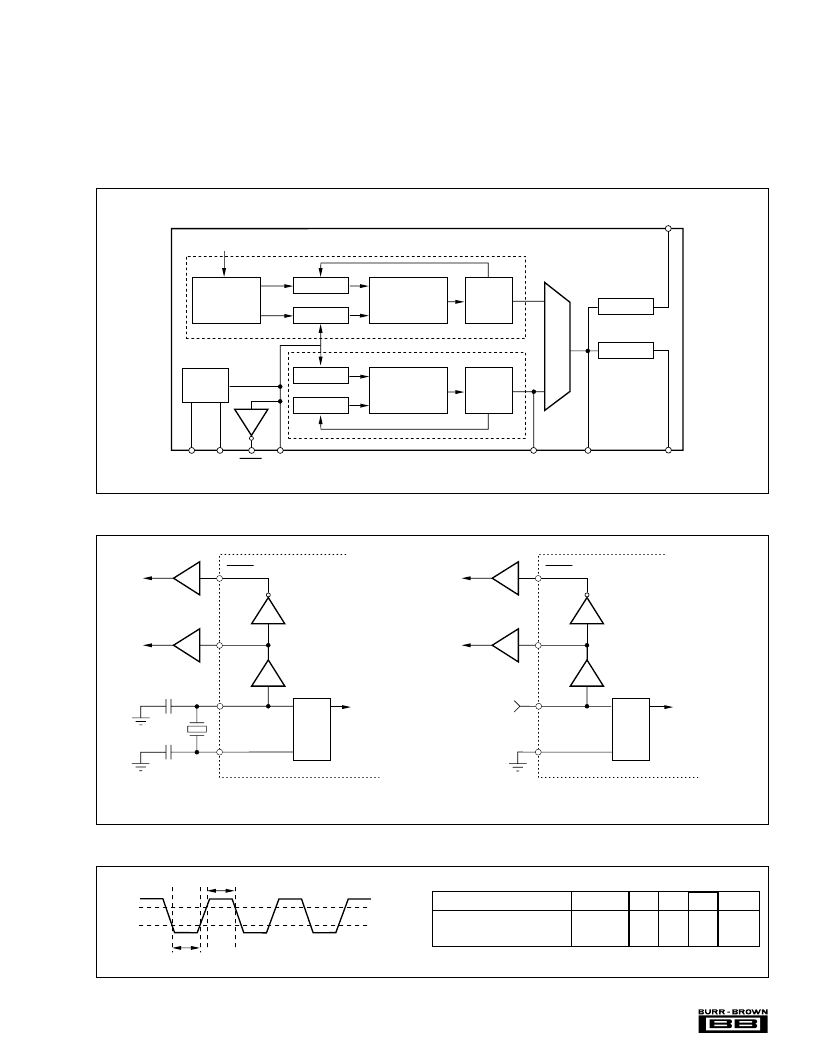

MASTER CLOCK AND SYSTEM CLOCK OUTPUT

The PLL1700 consists of a dual PLL clock and master clock

generator which generates four system clocks and two buff-

ered 27MHz clocks from a 27MHz master clock. Figure 1

shows the block diagram of the PLL1700. The PLL is

designed to accept a 27MHz master clock or crystal oscilla-

tor. The master clock can be either a crystal oscillator placed

between XT1 (pin 6) and XT2 (pin 5), or an external input

to XT1. If an external master clock is used, XT2 should be

connected to ground. Figure 2 illustrates possible system

clock connection options, and Figure 3 illustrates the 27MHz

master clock timing requirements.

FIGURE 1. Block Diagram of PLL1700.

FIGURE 2. Master Clock Generator Connection Diagram.

FIGURE 3. External Master Clock Timing Requirement.

t

XT1H

t

XT1L

2.0V

XT1

0.8V

DESCRIPTION

SYMBOL

MIN

TYP

MAX

UNITS

System Clock Pulse Width HIGH

System Clock Pulse Width LOW

t

XT1H

t

XT1L

15

15

ns

ns

OSC

Counter N

Counter M

Counter P

Counter Q

SCKO2

256f

S

SCKO1

33.8688MHz

SCKO4

768f

S

SCKO3

384f

S

Data

ROM

Frequency Control

PLL2

PLL1

Phase Detector

and

Loop Filter

VCO

VCO

Counter M

Counter N

Phase Detector

and

Loop Filter

MCKO

27MHz

MCKO

XT2

XT1

C

1

C

2

C

1

, C

2

= 10pF to 33pF

27MHz Internal

Master Clock

XTI

XT2

Crystal

OSC

Circuit

Xtal

PLL1700

MCKO

Buffer

External Clock

Crystal Resonator Connection

MCKO

Buffer

Crystal

OSC

Circuit

27MHz Internal

Master Clock

XT1

XT2

PLL1700

MCKO

Buffer

External Clock Input

MCKO

Buffer

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PLL1708DBQ | 3.3 V DUAL PLL MULTICLOCK GENERATOR |

| PLL1707DBQ | FF-SM Series, Type 3, Safety Mat, pressure sensitive, 750 x 750 mm2 [2.46 x 2.46 ft2] dimensions, nitrile [rubber] coating |

| PLL1707DBQR | FF-SM Series, Type 3, Safety Mat, pressure sensitive, 1000 x 500 mm2 [3.28 x 1.64 ft2] dimensions, aluminum coating |

| PLL1708DBQR | 3.3 V DUAL PLL MULTICLOCK GENERATOR |

| PLL1707 | 3.3 V DUAL PLL MULTICLOCK GENERATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PLL1700E/2K | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1700E/2KG4 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1700EG | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1700EG/2K | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| PLL1700EG/2KE6 | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 Multi-Clock Gen RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。