- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382368 > P82B96 (NXP Semiconductors N.V.) Dual bi-directional bus buffer PDF資料下載

參數(shù)資料

| 型號: | P82B96 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Dual bi-directional bus buffer |

| 中文描述: | 雙雙向總線緩沖器 |

| 文件頁數(shù): | 8/16頁 |

| 文件大小: | 217K |

| 代理商: | P82B96 |

Philips Semiconductors

Product data

P82B96

Dual bi-directional bus buffer

2004 Mar 26

8

frequency will be lower than calculated from the programmed clock

periods. In the example for 25 meters the clock is stretched 400 ns,

the falling edge of SCL is delayed 490 ns and the SDA rising edge is

delayed 570 ns. The required additional LOW period is

(490 + 570) = 1060 ns and the I

2

C-bus specifications already

include an allowance for a worst case bus risetime 0 to 70% of

425 ns. (The bus risetime can be 300 ns 30% to 70%, which means

it can be 425 ns 0–70%. The 25-meter cable delay times as quoted

already include all rise/fall times.) Therefore, the micro only needs to

be programmed with an addtional (1060 – 400 – 425) = 235 ns,

making a total programmed LOW period 1535 ns. The programmed

LOW will the be stretched by 400 ns to yield an actual bus LOW

time of 1935 ns, which, allowing the minimum HIGH period of

600 ns, yields a cycle period of 2535 ns or 394 kHz.

Note that in both the 100-meter and 250-meter examples the

capacitive loading on the I

2

C-buses at each end is within the

maximum allowed Standard mode loading of 400 pF, but exceeds

the Fast mode limit. This is an example of a ‘hybrid’ mode because it

relies on the response delays of Fast mode parts but uses

(allowable) Standard mode bus loadings with rise times that

contribute significantly to the system delays. The cables cause large

propagation delays so these systems need to operate well below the

400 kHz limit but illustrate how they can still exceed the 100 kHz

limit provided all parts are capable of Fast mode operation. The

fastest example illustrates how the 400 kHz limit can be exceeded

provided master and slave parts have delay specifications smaller

than the maximum allowed. Many Philips slaves have delays shorter

than 600 ns, but none have that guaranteed.

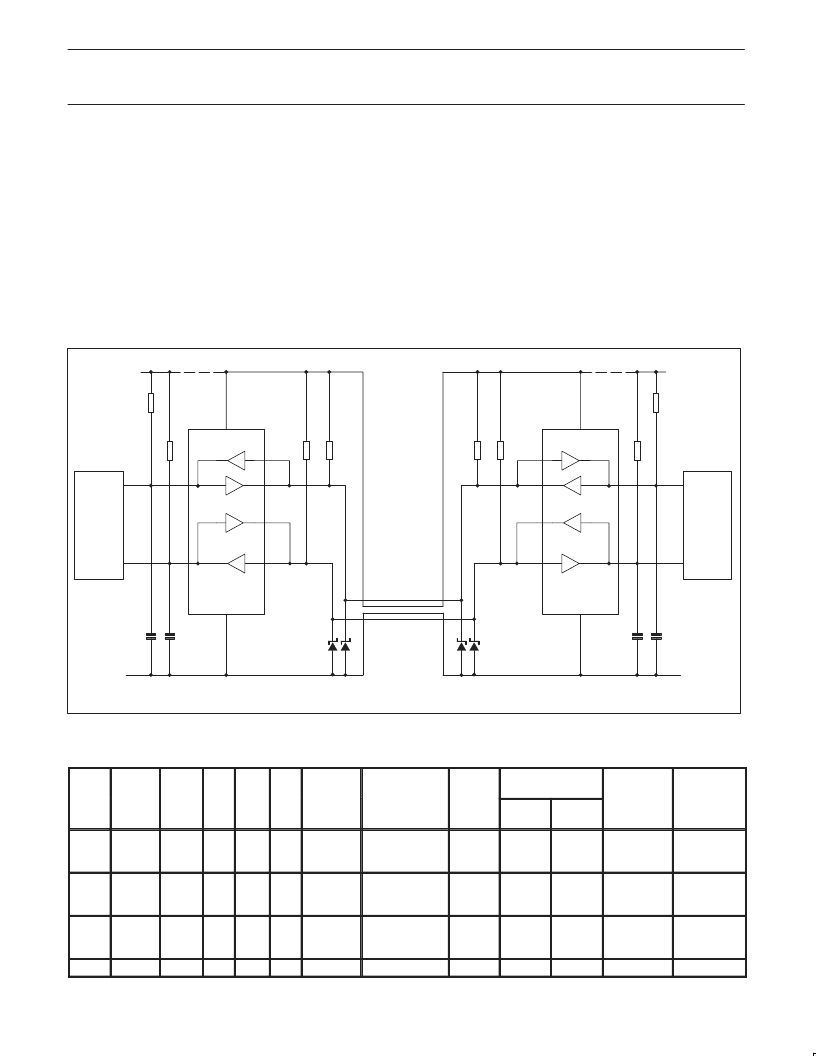

SCL

SDA

su01786

P82B96

V

CC

I

2

C

MASTER

GND

S

X

S

Y

R

X

T

X

R

Y

T

Y

V

CC1

V

CC2

SCL

SDA

P82B96

V

CC

I

2

C

SLAVE(S)

GND

S

X

S

Y

R

X

T

X

R

Y

T

Y

R1

R1

R2

R2

C2

C2

BAT54A

BAT54A

C2

C2

R2

R2

R1

R1

CABLE

PROPAGATION

DELAY

5 ns/m

+V CABLE DRIVE

Figure 5. Driving ribbon or flat telephone cables

EXAMPLES OF BUS CAPABILITY (refer to Figure 5)

+V

CC1

+V

+V

CC2

R1

R2

C2

(pF)

CABLE

LENGTH

CABLE

CABLE

DELAY

SET MASTER

NOMINAL SCL

EFFECTIVE

BUS

CLOCK

SPEED

MAXIMUM

SLAVE

RESPONSE

DELAY

CABLE

CAPACITANCE

HIGH

PERIOD

LOW

PERIOD

5 V

12 V

5 V

750

2.2 k

400

250 m

Not applicable

(delay based)

1.25

μ

s

600 ns

4000 ns

120 kHz

Normal spec.

400 kHz

parts

5 V

12 V

5 V

750

2.2 k

220

100 m

Not applicable

(delay based)

500 ns

600 ns

2600 ns

185 kHz

Normal spec.

400 kHz

parts

3.3 V

5 V

3.3 V

330

1 k

220

25 m

1 nF

125 ns

600 ns

1500 ns

390 kHz

Normal spec.

400 kHz

parts

3.3 V

5 V

3.3 V

330

1 k

100

3 m

120 pF

15 ns

600 ns

1000 ns

500 kHz

600 ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P82B96T | Dual bi-directional bus buffer |

| P82C150 | CAN Serial Linked I/O device SLIO with digital and analog port functions |

| P82C150AFT | CAN Serial Linked I/O device SLIO with digital and analog port functions |

| P82C150AHT | 22 PIN R/A MALE PRESSFIT ATCA ZONE 1 CON |

| P82C605 | System Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P82B96_08 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual bidirectional bus buffer |

| P82B96_09 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL BIDIRECTIONAL BUS BUFFER |

| P82B96D | 功能描述:緩沖器和線路驅(qū)動器 Dual Bidirectional Bus Buffer RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| P82B96DG4 | 功能描述:緩沖器和線路驅(qū)動器 Dual Bidirectional Bus Buffer RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| P82B96DGKR | 功能描述:緩沖器和線路驅(qū)動器 Dual Bidirectional Bus Buffer RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。