- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384801 > OX16C954 (Electronic Theatre Controls, Inc.) High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface PDF資料下載

參數(shù)資料

| 型號(hào): | OX16C954 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface |

| 中文描述: | UART的高性能四路128字節(jié)的FIFO英特爾/摩托羅拉總線接口 |

| 文件頁(yè)數(shù): | 12/54頁(yè) |

| 文件大?。?/td> | 529K |

| 代理商: | OX16C954 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Data Sheet Revision 1.0

Page 12

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

TQFP

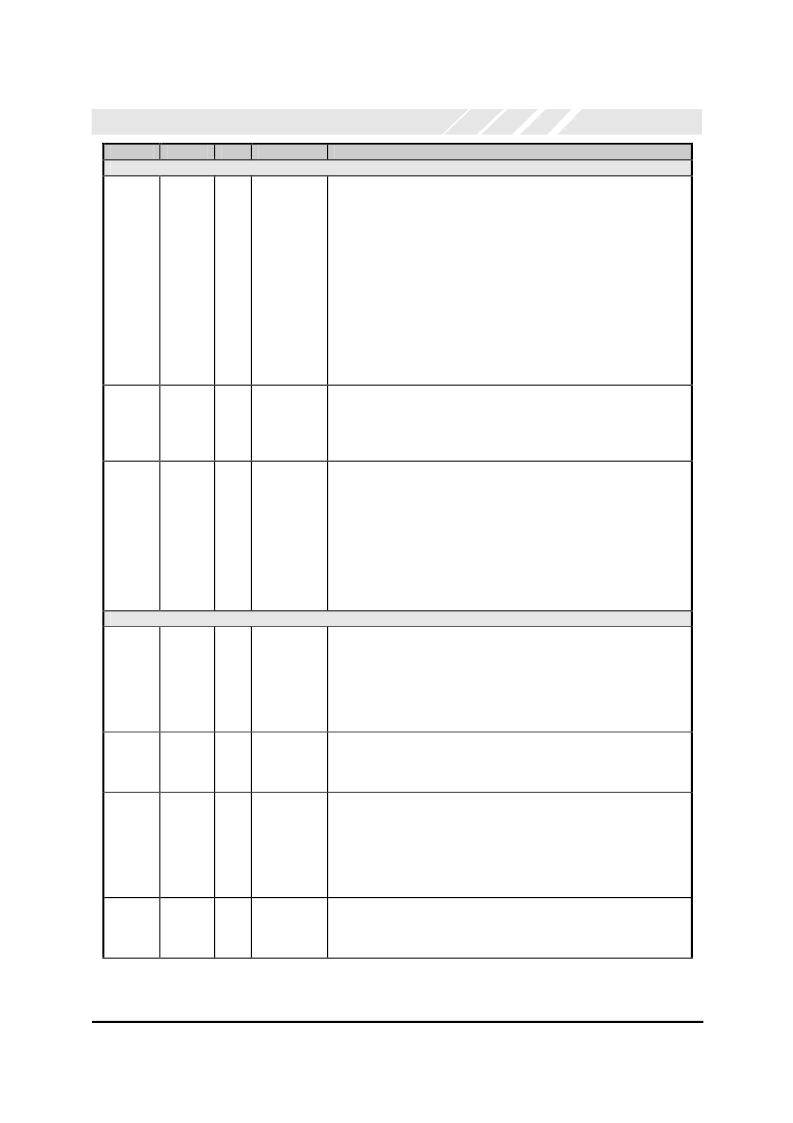

Serial Port Pins Contd.

79

62

39

22

79

62

39

22

10

PLCC

Dir

1

Name

Description

60

44

26

10

60

44

26

I

I

I

I

I

I

I

I

DSR[3]#

DSR[2]#

DSR[1]#

DSR[0]#

RxClkIn[3]

RxClkIn[2]

RxClkIn[1]

RxClkIn[0]

DCD[3]#

DCD[2]#

DCD[1]#

DCD[0]#

RI[3]#

RI[2]#

RI[1]#

RI[0]#

Ext_CK[3]

Ext_CK[2]

Ext_CK[1]

Ext_CK[0]

Active-low modem“data-set-ready” input, for each uart respectively.

If automated DSR#flow control is enabled for the corresponding UART

channel, upon deassertion of the channel’s DSR#pin, the transmtter will

complete the current character and enter the idle mode until the DSR#pin

is reasserted. Note: flow control characters are transmtted regardless of

the state of the DSR#pin. The state of this pin is reflected in bit 5 of the

MSR.

It can also be used as a general-purpose input

.

External receiver clock for isochronous applications for each uart

respectively. Selected when CKS[1:0] = ‘01’.

2

59

42

19

61

43

27

9

I

I

I

I

Active-low modemData-Carrier-Detect input, for each uart respectively.

The state of this pin is reflected in bit 7 of the MSR.

It can also be used

as a general-purpose input

.

3

58

43

18

3

58

43

18

62

42

28

8

62

42

28

8

I

I

I

I

I

I

I

I

Active-low modemRing-Indicator input, for each uart respectively.

The state of this pin is reflected in bit 6 of the MSR.

It can also be used

as a general-purpose input

. RI can be configured as tx and rx for a 1x

clock in isochronous operation.

External transmtter clock for each uart respectively. This clock can be

used by the transmtter (and by the receiver indirectly) when CKS[6] = ‘1’.

Interrupt & DMA Pins

1

61

41

21

No pin

No pin

No pin

No pin

O

O

O

O

TXRDY3#

TXRDY2#

TXRDY1#

TXRDY0#

Signal for the DMA transfer of transmtter data, for Uart 3.

Signal for the DMA transfer of transmtter data, for Uart 2.

Signal for the DMA transfer of transmtter data, for Uart 1.

Signal for the DMA transfer of transmtter data, for Uart 0.

There are two modes of DMA signalling described in section 8.1

Signal for the DMA transfer of transmtter data.

This pin is the wire ”O(jiān)R-ed” function of the TXRDY#signals of all

channels.

Signal for the DMA transfer of receiver data, for Uart 3.

Signal for the DMA transfer of receiver data, for Uart 2.

Signal for the DMA transfer of receiver data, for Uart 1.

Signal for the DMA transfer of receiver data, for Uart 0.

There are two modes of DMA signalling described in section 8.1

Signal for DMA transfer of received data.

This pin is the wire ”O(jiān)R-ed” function of the RXRDY#signals of all

channels.

55

39

O

TXRDY#

80

60

40

20

No pin

No pin

No pin

No pin

O

O

O

O

RXRDY3#

RXRDY2#

RXRDY1#

RXRDY0#

54

38

O

RXRDY#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OX16C954-PCC60-B | High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface |

| OX16C954-TQC60-B | High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface |

| OX16CF950 | LOW COST ASYNCHRONOUS 16 BIT CARD |

| OX2000A | OCXO |

| OX2020A | OCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OX16C954B | 制造商:PLX 制造商全稱:PLX 功能描述:High Performance Quad UART |

| OX16C954-PCC60-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface |

| OX16C954-PLBG | 制造商:Oxford Semiconductor 功能描述:IC UART 4CH SMD PLCC68 954 |

| OX16C954-TQBG | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI High performance quad UART RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| OX16C954-TQC60-B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。