- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄299581 > ORT82G5-2BM680 (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 380000 GATES, PBGA680 PDF資料下載

參數(shù)資料

| 型號(hào): | ORT82G5-2BM680 |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| 封裝: | PLASTIC, BGA-680 |

| 文件頁(yè)數(shù): | 25/110頁(yè) |

| 文件大小: | 1459K |

| 代理商: | ORT82G5-2BM680 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)

Lattice Semiconductor

21

Data Sheet

January 25, 2002

8b/10b SERDES Backplane Interface FPSC

ORCA ORT82G5 1.0-1.25/2.0-2.5/3.125-3.5 Gbits/s

Backplane Transceiver Core Detailed Description (continued)

8b/10b Encoding

The 8b/10b encoder encodes the incoming 8-bit data into a 10-bit format according to the FC-PH ANSI

X3.230:1994 standard. Input pins SRBDx<7:0> (where x is a placeholder for one of the letters, A—D) are used for

8 bit unencoded data and SRBDx<8> is used as the K_control input to indicate whether the 8 data bits need to be

encoded as special characters (K_control = 1) or as data characters (K_control = 0). When the encoder is

bypassed SRBDx<9:0>serve as the data bits for the 10-bit encoded data. The following table shows two different

codings that are possible for each data value and are shown as encoded word(+) and encoded word (-). The trans-

mitter selects between (+) and (-) encoded word based on calculated disparity of the present data.

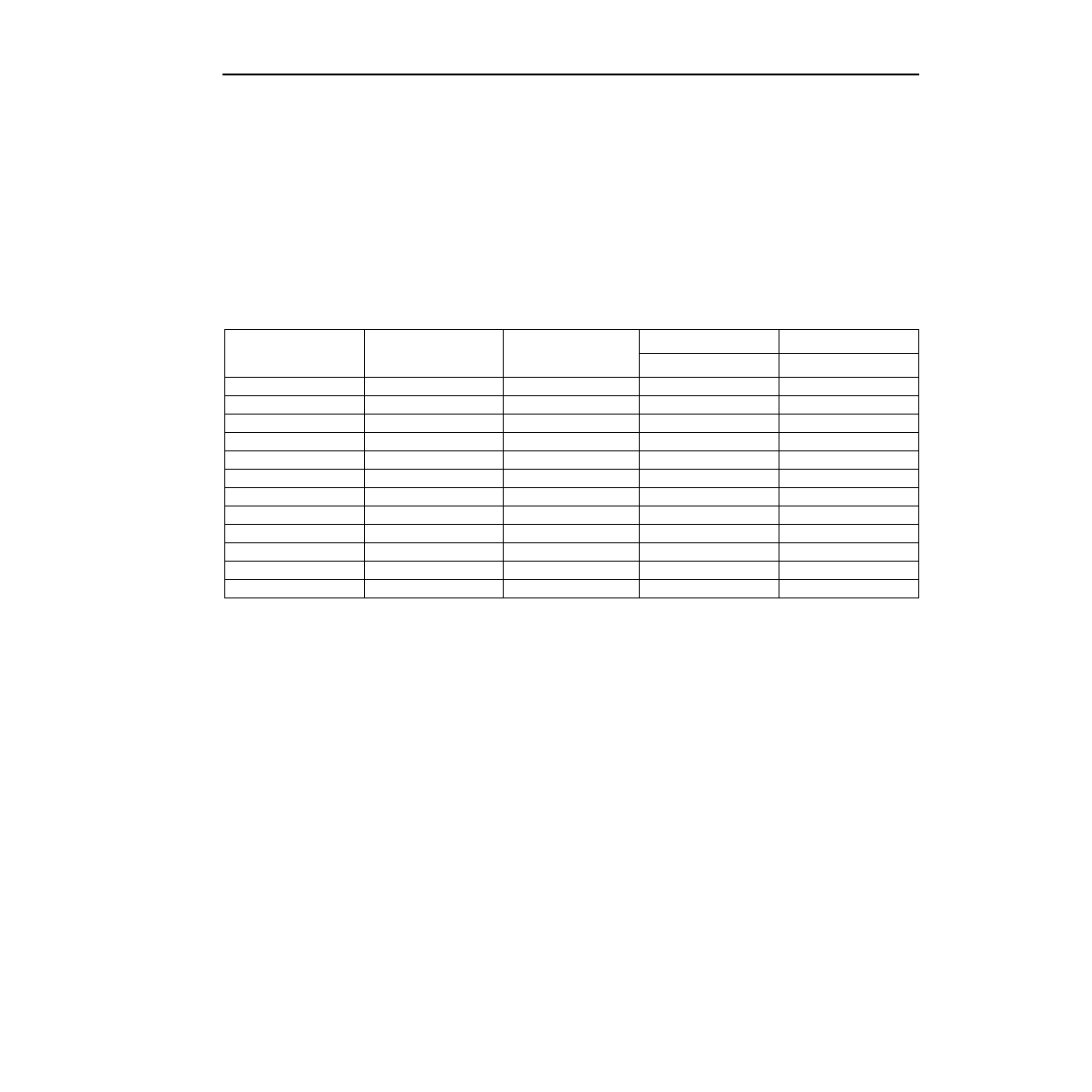

Table 3. Valid Special Characters

Within the denition of the 8b/10b transmission code, the bit positions of the 10-bit encoded transmission charac-

ters are labeled as a, b, c, d, e, i, f, g, h, and j in that order. Bit a corresponds to SRBDx[0], bit b to SRBDx[1], bit c

to SRBDx[2], bit d to SRBDx[3], bit e to SRBDx[4], bit i to SRBDx[5], bit f to SRBDx[6], bit g to SRBDx[7], bit h to

SRBDx[8], and bit j to SRBDx[9]. The data SRBDx[9:0] is transmitted serially with SRBDx[0] transmitted rst and

SRBDx[9] transmitted last.

For an 8-bit unencoded data, the 8-bit unencoded data SRDBx[7:0] is represented as HGF EDCBA SRDBx[8] rep-

resents the K_CTRL bit and SRDBx[9] is unused. SRBDx[0] is still transmitted rst and SRBDx[9] transmitted last.

8b/10b Decoding

A 8b/10b decoder block is available to allow for receiving data that has been encoded using a standard 8B/10B

encoder. This encoding/decoding scheme also allows for the transmission of special characters and allows for

error detection.

Clock recovery for the 8B/10B decoder is performed by the SERDES block for each of the eight receive channels.

This recovered data is then aligned to a 10-bit word boundary by detecting and aligning to the comma codeword.

Word alignment is done to either polarity of this codeword. The 10-bit code word is passed to the decoder, which

provides an 8-bit byte of data and a SBYTSYNC signal.

K character

HGF EDCBA

765 43210

K control

Encoded Word (–)

Encoded Word (+)

abcdei fghj

K28.0

000 11100

1

001111 0100

110000 1011

K28.1

001 11100

1

001111 1001

110000 0110

K28.2

010 11100

1

001111 0101

110000 1010

K28.3

011 11100

1

001111 0011

110000 1100

K28.4

100 11100

1

001111 0010

110000 1101

K28.5

101 11100

1

001111 1010

110000 0101

K28.6

110 11100

1

001111 0110

110000 1001

K28.7

111 11100

001111 1000

110000 0111

K23.7

111 10111

1

111010 1000

000101 0111

K27.7

111 11011

1

110110 1000

001001 0111

K29.7

111 11101

1

101110 1000

010001 0111

K30.7

111 11110

1

011110 1000

100001 0111

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ORT82G5-3BM680 | FPGA, 1296 CLBS, 380000 GATES, PBGA680 |

| OS10040280G-012 | FIBER OPTIC RECEIVER, 1290-1600nm, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-10-X-9-M-3-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 10.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-13-9-F-1-05-FA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, FC/APC CONNECTOR |

| OT-WBSC-Y-A-50-X-9-O-1-99-SA | FIBER OPTIC SPLITTER/COUPLER, 1X2PORT, 50.0, PANEL MOUNT, SC/APC CONNECTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ORT82G5-2BM680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-2BM680I | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-2F680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-2F680I | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 2.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-2FN680C | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。