- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299575 > OR3T307S240-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 196 CLBS, 48000 GATES, PQFP240 PDF資料下載

參數(shù)資料

| 型號: | OR3T307S240-DB |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| 封裝: | PLASTIC, SQFP-240 |

| 文件頁數(shù): | 157/203頁 |

| 文件大小: | 1368K |

| 代理商: | OR3T307S240-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁當前第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁

Lattice Semiconductor

57

Data Sheet

November 2006

ORCA Series 3C and 3T FPGAs

Special Function Blocks (continued)

The external test (EXTEST) instruction allows the inter-

connections between ICs in a system to be tested for

opens and stuck-at faults. If an EXTEST instruction is

performed for the system shown in Figure 36, the con-

nections between U1 and U2 (shown by nets a, b, and

c) can be tested by driving a value onto the given nets

from one device and then determining whether the

same value is seen at the other device. This is deter-

mined by shifting 2 bits of data for each pin (one for the

output value and one for the 3-state value) through the

BSR until each one aligns to the appropriate pin. Then,

based upon the value of the 3-state signal, either the

I/O pad is driven to the value given in the BSR, or the

BSR is updated with the input value from the I/O pad,

which allows it to be shifted out TDO.

The SAMPLE/PRELOAD instruction is useful for sys-

tem debugging and fault diagnosis by allowing the data

at the FPGA’s I/Os to be observed during normal

operation or written during test operation. The data for

all of the I/Os is captured simultaneously into the BSR,

allowing them to be shifted-out TDO to the test host.

Since each I/O buffer in the PICs is bidirectional, two

pieces of data are captured for each I/O pad: the value

at the I/O pad and the value of the 3-state control sig-

nal. For preload operation, data is written from the BSR

to all of the I/Os simultaneously.

There are ve

ORCA-dened instructions. The PLC

scan rings 1 and 2 (PSR1, PSR2) allow user-dened

internal scan paths using the PLC latches/FFs. The

RAM_Write Enable (RAM_W) instruction allows the

user to serially congure the FPGA through TDI. The

RAM_Read Enable (RAM_R) allows the user to read

back RAM contents on TDO after conguration. The

IDCODE instruction allows the user to capture a 32-bit

identication code that is unique to each device and

serially output it at TDO. The IDCODE format is shown

in Table 14.

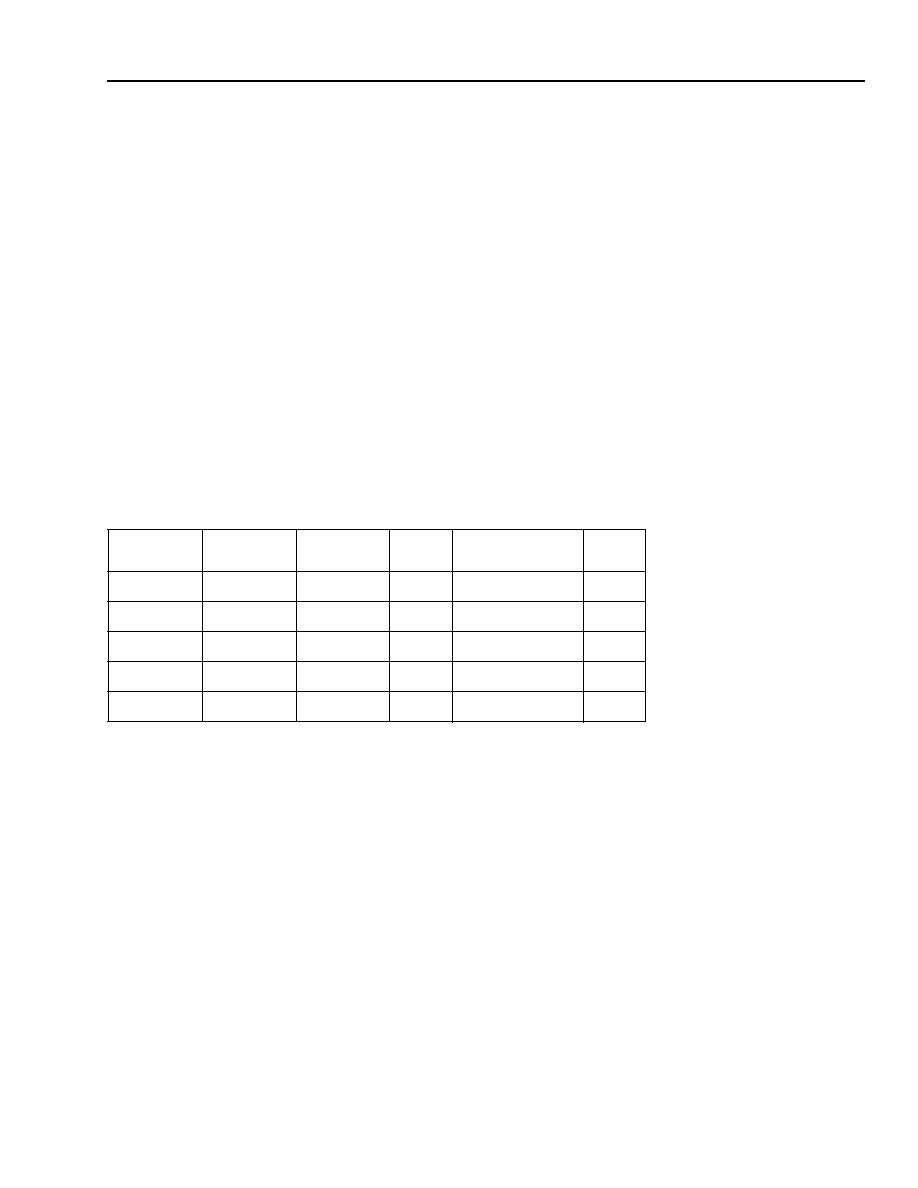

Table 14. Boundary-Scan ID Code

* PLC array size of FPGA, reverse bit order.

Note: Table assumes version 0.

Device

Version

(4 bits)

Part

*

(10 bits)

Family

(6 bits)

Manufacturer

(11 bits)

LSB

(1 bit)

OR3T20

0000

0011000000 110000

00000011101

1

OR3T30

0000

0111000000 110000

00000011101

1

OR3T55

0000

0100100000 110000

00000011101

1

OR3C/T80

0000

0110100000 110000

00000011101

1

OR3T125

0000

0011100000 110000

00000011101

1

Select

devices

have

been

discontinued.

See

Ordering

Information

section

for

product

status.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3T556PS240-DB | FPGA, 324 CLBS, 80000 GATES, PQFP240 |

| OR3T806PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T807PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T55-4BA256I | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

| OR3T55-4BA256 | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3T30-7S240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T55-4BA256I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T55-4PS240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。