- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄299576 > OR3T125-4B432 FPGA, 784 CLBS, 92000 GATES, PBGA432 PDF資料下載

參數(shù)資料

| 型號(hào): | OR3T125-4B432 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 784 CLBS, 92000 GATES, PBGA432 |

| 封裝: | BGA-432 |

| 文件頁(yè)數(shù): | 1/210頁(yè) |

| 文件大小: | 2138K |

| 代理商: | OR3T125-4B432 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)

ORCA Series 3

Field-Programmable Gate Arrays

Preliminary Data Sheet, Rev. 1

September 1998

Features

T High-performance, cost-effective, 0.35 m (OR3C) and

0.3 m (OR3T) 4-level metal technology, with a migra-

tion plan to 0.25 m technology (4- or 5-input look-up

table delay of 1.7 ns with -5 speed grade in 0.35 m).

T Up to 186,000 usable gates in 0.3 m, expanding to

320,000 usable gates in 0.25 m.

T Up to 452 user I/Os. (OR3Txxx I/Os are 5 V tolerant to

allow interconnection to both 3.3 V and 5 V devices,

selectable on a per-pin basis.)

T Pin selectable I/O clamping diodes provide 5 V or 3.3 V

PCI compliance and 5 V tolerance on OR3Txxx devices.

T New twin-quad programmable function unit (PFU) archi-

tecture with eight 16-bit look-up tables (LUTs) per PFU,

organized in two nibbles for use in nibble- or byte-wide

functions. Allows for mixed arithmetic and logic functions

in a single PFU.

T Nine user registers per PFU, one following each LUT,

plus one extra. All have programmable clock enable and

local set/reset, plus a global set/reset that can be dis-

abled per PFU.

T New flexible input structure (FINS) of the PFUs provides

a routability enhancement for LUTs with shared inputs

and the logic flexibility of LUTs with independent inputs.

T Fast-carry logic and routing to adjacent PFUs for

nibble-, byte-wide, or longer arithmetic functions, with

the new option to register the PFU carry-out.

T New softwired LUTs (SWL) allow fast cascading of up to

three levels of LUT logic in a single PFU for up to 40%

speed improvement.

T New supplemental logic and interconnect cell (SLIC)

provides 3-statable buffers, up to 10-bit decoder, and

PAL*-like AND-OR with optional INVERT in each pro-

grammable logic cell (PLC).

T Abundant hierarchical routing resources based on rout-

ing two data nibbles and two control lines per set provide

for faster place and route implementations and less rout-

ing delay.

T TTL or CMOS input levels programmable per pin for the

OR3Cxx (5.0 V) devices.

T Individually programmable drive capability: 12 mA sink/

6 mA source or 6 mA sink/3 mA source.

T Built-in boundary scan (IEEE

1149.1 JTAG) and

3-state all I/O pins (TS_ALL) testability functions.

T Enhanced system clock routing for low skew, high-speed

clocks originating on-chip or at any I/O.

T Up to four new ExpressCLK inputs allow extremely fast

clocking of signals on- and off-chip plus access to inter-

nal general clock routing.

T New StopCLK feature to glitchlessly stop/start Express-

CLK

s independently by user command.

T New programmable I/O (PIO) has:

— Fast-capture input latch and input flip-flop (FF)

latch for reduced input setup time and zero hold time.

— Capability to (de)multiplex I/O signals.

— Fast access to SLIC for decodes and

PAL-like

functions.

— Output FF and two-signal function generator to

reduce CLK to output propagation delay.

— Fast open-drain drive capability.

— Capability to register 3-state enable signal.

*

PAL is a trademark of Advanced Micro Devices, Inc.

IEEE is a registered trademark of The Institute of Electrical and

Electronics Engineers, Inc.

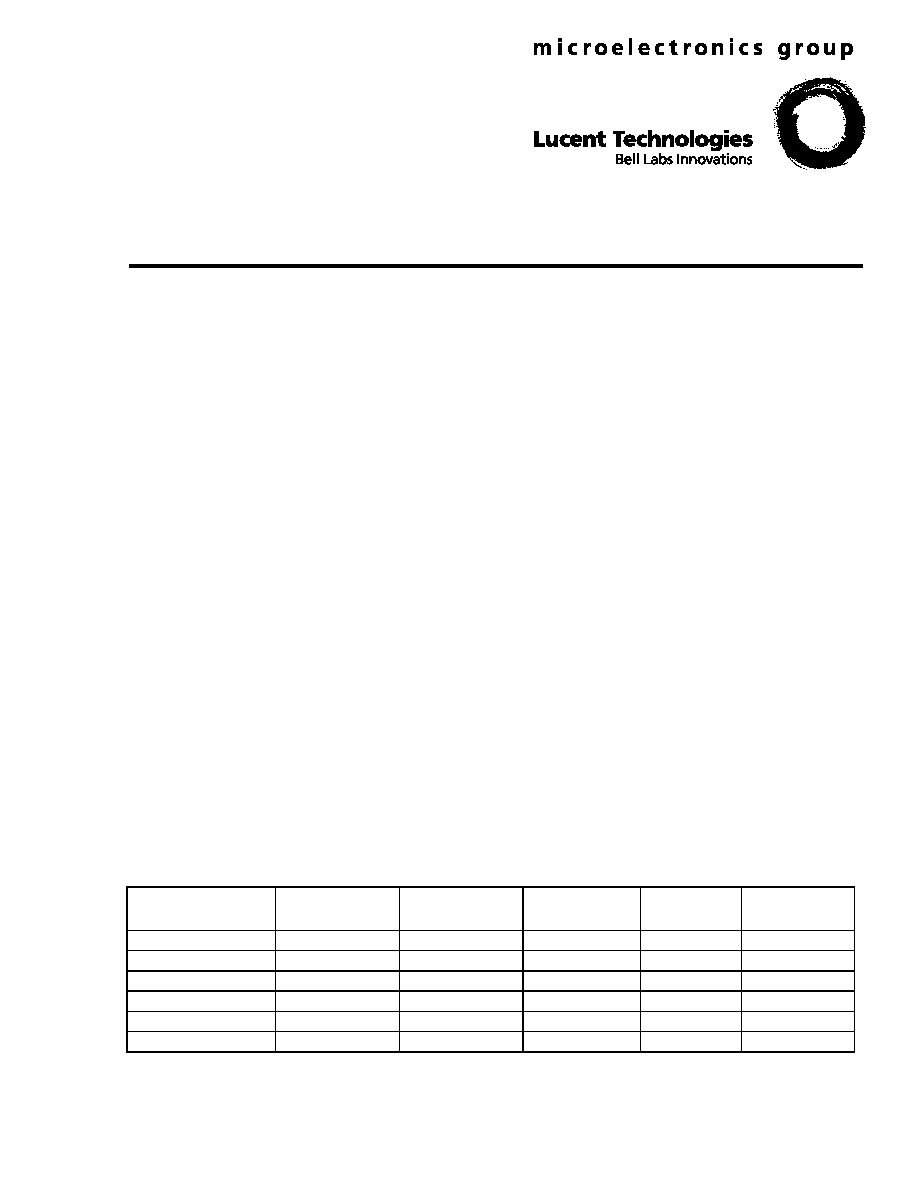

Table 1. ORCA Series 3 FPGAs

The usable gate counts range from a logic-only gate count to a gate count assuming 30% of the PFUs/SLICs being used as RAMs.

The logic-only gate count includes each PFU/SLIC (counted as 108 gates per PFU/SLIC), including 12 gates per LUT/FF pair (eight per

PFU), and 12 gates per SLIC/FF pair (one per PFU). Each of the four PIOs per PIC is counted as 16 gates (two FFs, fast-capture latch,

output logic, CLK drivers, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing

a 32 x 4 RAM (or 512 gates) per PFU.

Device

Usable Gates

Max

Registers

Max User

RAM Bits

Max

User I/Os

Array Size

OR3T20

18K—36K

1872

18K

192

12 x 12

OR3T30

24K—48K

2436

25K

224

14 x 14

OR3C/T55

40K—80K

3780

41K

288

18 x 18

OR3C/T80

58K—116K

5412

62K

352

22 x 22

OR3T125

92K—186K

8400

100K

448

28 x 28

OR3T165

120K—244K

10752

131K

512

32 x 32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3T125-4B600 | FPGA, 784 CLBS, 92000 GATES, PBGA600 |

| OR3T125-4BA352I | FPGA, 784 CLBS, 92000 GATES, PBGA352 |

| OR3T125-4BA352 | FPGA, 784 CLBS, 92000 GATES, PBGA352 |

| OR3T125-5B432 | FPGA, 784 CLBS, 92000 GATES, PBGA432 |

| OR3T125-5B600 | FPGA, 784 CLBS, 92000 GATES, PBGA600 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3T125-4BC432I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T125-4BC600I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T125-4PS208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T125-4PS240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| OR3T125-5BA352 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。