- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC2105CDG66 (MOTOROLA INC) 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms PDF資料下載

參數(shù)資料

| 型號: | MPC2105CDG66 |

| 廠商: | MOTOROLA INC |

| 元件分類: | SRAM |

| 英文描述: | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| 中文描述: | 64K X 72 CACHE SRAM MODULE, 9 ns, PDMA178 |

| 文件頁數(shù): | 12/18頁 |

| 文件大小: | 229K |

| 代理商: | MPC2105CDG66 |

MPC2105C

MPC2106C

12

MOTOROLA FAST SRAM

TAG RAM AC OPERATING CONDITIONS AND CHARACTERISTICS

(VCC = 5.0 V

±

5%, TA = 0 to + 70

°

C, Unless Otherwise Noted)

Input Timing Measurement Reference Level

Input Pulse Levels

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Rise/Fall Time

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 V

. . . . . . . . . . . . . . .

0 to 3.0 V

3 ns

Output Timing Measurement Reference Level

Output Load

. . . . . . . . . . . . . . . . . .

1.5 V

. . . . . . . . . . . . .

Figure 1 Unless Otherwise Noted

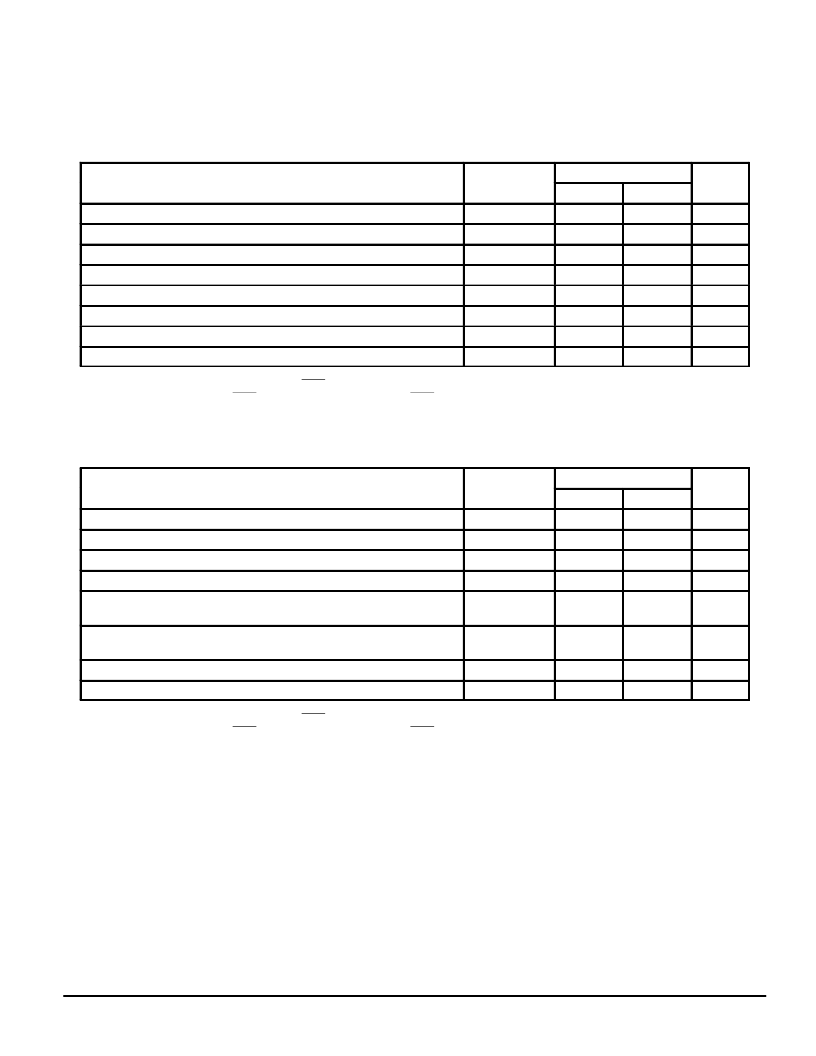

TAG RAM READ CYCLE

(See Notes 1 through 4)

Tag RAM

Parameter

Symbol

Min

Max

Unit

Clock Access Time

tKHQV

tGLQV

tGLQX

tGHQZ

tAXSX

tAVSV

tAVQX

tAVQV

—

10

ns

Output Enable to Output Valid

—

8

ns

Output Enable to Output Active

0

—

ns

Output Disable to Q High–Z

1

6

ns

Status Bit Hold from Address Change

3

—

ns

Address Access Time Status Bits

—

10

ns

Tag Bit Hold from Address Change

3

—

ns

Address Access Time Tag Bits

—

12

ns

NOTES:

1. Setup and hold times, W (write) refers to TWE.

2. A read cycle is defined by TWE high. A write cycle is defined by TWE low.

3. Maximum access times are guaranteed for all possible MC68040 and PowerPC external bus cycles.

4. Tag reads are asynchronous.

TAG RAM WRITE CYCLE

(See Notes 1 through 4)

Tag RAM

Parameter

Symbol

Min

Max

Unit

Cycle Time

tKHKH

tKHKL

tKLKH

tKHQX

tAVKH

tWVKH

15

—

ns

Clock High Pulse Width

4.5

—

ns

Clock Low Pulse Width

4.5

—

ns

Clock High to Output Active

1.5

—

ns

Setup Times

Address

Write

3

—

ns

Hold Times

Address

Write

tKHAX

tKHWX

1.5

—

ns

Status Output Hold

tKHSX

tKHSV

0

—

ns

Clock High to Status Bits Valid

—

9

ns

NOTES:

1. Setup and hold times, W (write) refers to TWE.

2. A read cycle is defined by TWE high. A write cycle is defined by TWE low.

3. Maximum access times are guaranteed for all possible MC68040 and PowerPC external bus cycles.

4. Tag writes are synchronous.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC2105C | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106ASG66 | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106SG66 | 256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2105A | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106CDG66 | 512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC2105PDG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB/512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2105SG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256KB and 512KB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106ASG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106BSG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

| MPC2106CDG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:512KB and 1MB BurstRAM Secondary Cache Modules for PowerPC PReP/CHRP Platforms |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。