- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382301 > MC4GH02GNMCA-2SA00 (SAMSUNG SEMICONDUCTOR CO. LTD.) SAMSUNG MultiMediaCard PDF資料下載

參數(shù)資料

| 型號(hào): | MC4GH02GNMCA-2SA00 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | SAMSUNG MultiMediaCard |

| 中文描述: | 三星多媒體 |

| 文件頁(yè)數(shù): | 75/102頁(yè) |

| 文件大小: | 1384K |

| 代理商: | MC4GH02GNMCA-2SA00 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)當(dāng)前第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

MultiMediaCard

TM

75

Sep.22.2005

Revision 0.3

6.14 Data Write

Single Block Write

The host selects the card for data write operation by CMD7.

The host sets the valid block length for block oriented data transfer (a stream write mode is also available) by CMD16.

The basic bus timing for a write operation is given in Figure 6-15. The sequence starts with a single block write command

(CMD24) which determines (in the argument field) the start address. It is responded by the card on the CMD line as usual.

The data transfer from the host starts N

WR

clock cycles after the card response was received.

The data is suffixed with CRC check bits to allow the card to check it for transmission errors. The card sends back the

CRC check result as a CRC status token on DAT0. In the case of transmission error, occurring on any of the active data

lines, the card sends a negative CRC status (‘101’) on DAT0. In the case of successful transmission, over all active data

lines, the card sends a positive CRC status (‘010’) on DAT0 and starts the data programming procedure

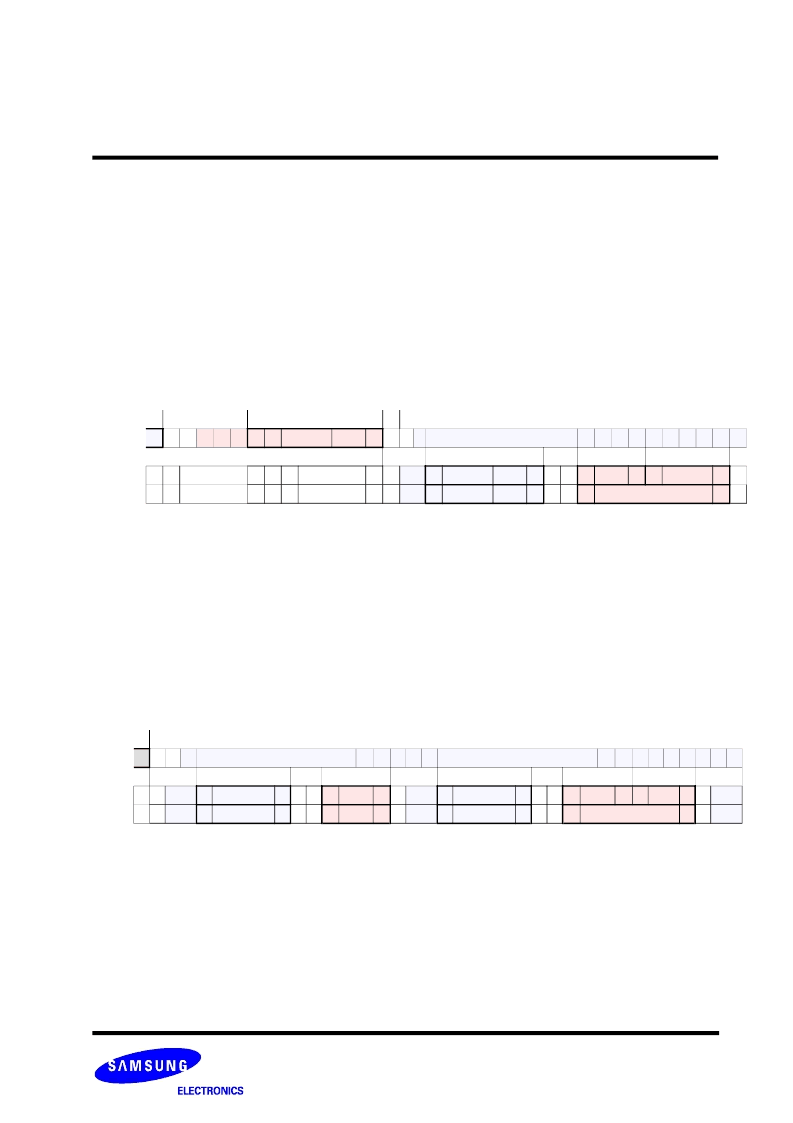

Figure 6-15 : Block Write Command Timing

If the card does not have a free data receive buffer, the card indicates this condition by pulling down the data line DAT0 to

LOW. The card stops pulling down DAT0 as soon as at least one receive buffer for the defined data transfer block length

becomes free. This signalling does not give any information about the data write status which must be polled by the host.

Multiple Block Write

In multiple block write mode, the card expects continuous flow of data blocks following the initial host write command. The

data flow is terminated by a stop transmission command (CMD12). Figure 6-16 describes the timing of the data blocks

with and without card busy signal.

Host cmnd

→ ←

N

CR

cycles

→←

Card response

→

CMD

E Z Z P * P S T

Content

CRC E Z Z P

* * * * * * * * * * * *

P P P P P P P P P P

←

CRC status

→

←

Busy

→

CRC E Z Z S Status E S

CRC E Z Z X

* * * * * * * * * * * *

←

N

WR

→←

Write data

→

Z Z P * P S

content

Z Z P * P S

content

DAT0

DAT1-7

Z Z

Z Z

* * * * * *

* * * * * *

Z Z Z

Z Z Z

* * * * *

* * * * *

L * L

E Z

X Z

Card Rsp

→

CMD

E Z Z P

←

N

WR

→ ←

Write data

→

Z Z P * P S Data

+ CRC

E Z Z S Status E Z P * P S Data

+ CRC

E Z Z S Status E S L * L E Z P * P

Z Z P * P S Data

+ CRC

E Z Z X * * * X Z P * P S Data

+ CRC

E Z Z X * * * * * * * * * * X Z P * P

* * * * * * * * * * * * * * * *

P P P P P

* * * * * * * * * * * * * * * *

P

P P P P P P P P

←

CRC status

→

←

Busy

→ ←

N

WR

→

←

CRC status

→

←

N

WR

→ ←

Write data

→

DAT0

DAT1-7

Figure 6-16 : Multiple Block Write Timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC206 | THIN SMD LOW/MEDIUM-FREQUENCY CRYSTAL UNIT |

| MC2300 | Navigator Motion Processor |

| MC26LS30 | Dual Differential Quad Single-Ended (EIA-423-A) Line Drivers |

| MC26LS30D | CABLE GLAND, PG29 |

| MC26LS30DR2 | Dual Differential Quad Single-Ended (EIA-423-A) Line Drivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC4M | 制造商:G & J HALL 功能描述:STEP DRILL MULTICUT 4-12MM X 2MM 制造商:G & J HALL 功能描述:STEP DRILL, MULTICUT, 4-12MM X 2MM |

| MC-4-MALE | 制造商:Multi-Contact USA 功能描述: |

| MC4MANUAL | 制造商:Omron Corporation 功能描述: |

| MC-4R128CEE6B | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:Direct Rambus DRAM RIMM Module 128M-BYTE 64M-WORD x 16-BIT |

| MC-4R128CEE6B-653 | 制造商:NEC 制造商全稱(chēng):NEC 功能描述:Direct Rambus DRAM RIMM Module 128M-BYTE 64M-WORD x 16-BIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。