- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369586 > KP80524NY450128 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | KP80524NY450128 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 79/81頁 |

| 文件大小: | 598K |

| 代理商: | KP80524NY450128 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當(dāng)前第79頁第80頁第81頁

Mobile Intel

Celeron Processor (0.18μ) in BGA2 and Micro-PGA2 Packages

Order Number#249563-001

Datasheet

79

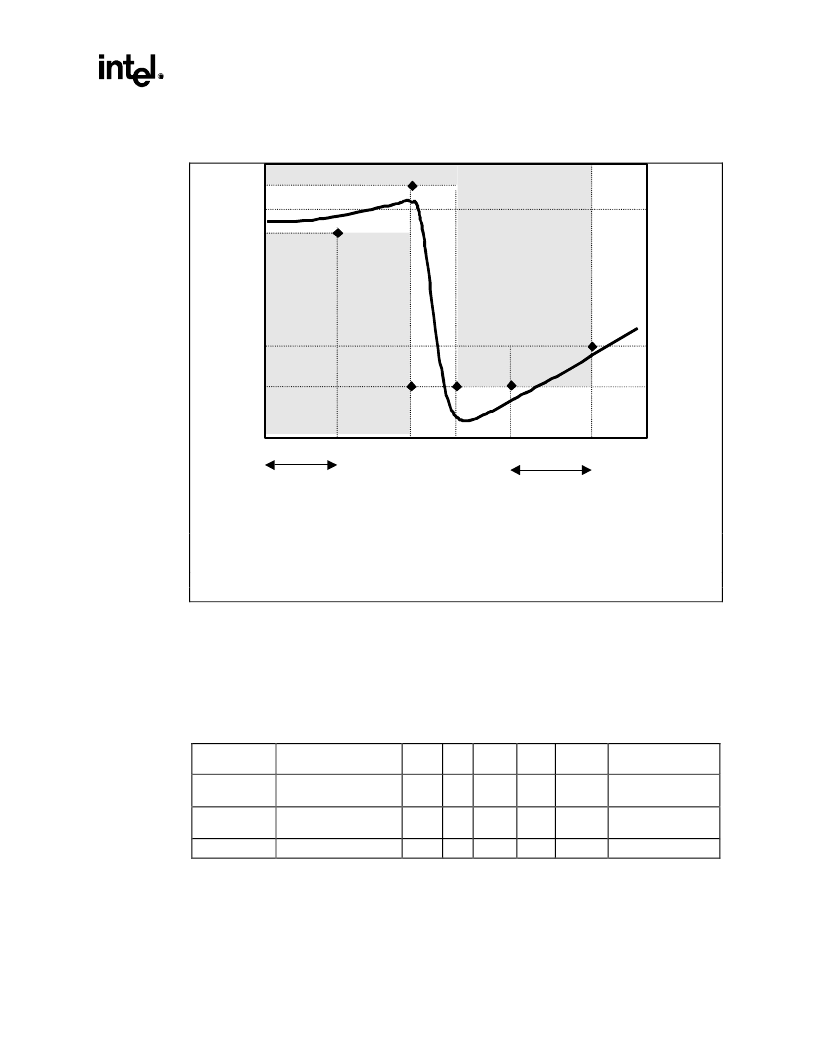

Figure 25. PLL Filter Specifications

0 dB

-28 dB

-34 dB

0.2 dB

forbidden

zone

x dB

forbidden

zone

1 MHz

66 MHz

fcore

fpeak

1 Hz

DC

passband

high frequency

band

x = 20.log[(Vcct-60 mV)/Vcct]

NOTES:

1. Diagram is not to scale

2. No specification for frequencies beyond fcore.

3. Fpeak, if existent, should be less than 0.05 MHz.

A.3

Recommendation for Mobile Systems

The following LC components are recommended. The tables will be updated as other suitable

components and specifications are identified.

Table 41. PLL Filter Inductor Recommendations

Inductor

Part Number

Value

Tol

SRF

Rated

I

DCR

Min Damping R

needed

L1

TDK MLF2012A4R7KT

4.7

μ

H 10% 35 MHz 30 mA 0.56

(1

max)

0

L2

Murata LQG21N4R7K10 4.7

μ

H 10% 47 MHz 30 mA 0.7

(+/-

50%)

0

L3

Murata LQG21C4R7N00 4.7

μ

H 30% 35 MHz 30 mA 0.3

max

0.2

(assumed)

NOTE:

Minimum damping resistance is calculated from 0.35

– DCR

min

. From vendor provided data, L1 and

L2 DCR

min

is 0.4

and 0.5

respectively, qualifying them for zero required trace resistance. DCR

min

for L3 is not known and is assumed to be 0.15

. There may be other vendors who might provide

parts of equivalent characteristics and the OEMs should consider doing their own testing for selecting

their own vendors.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RH8053GC017512 | Microprocessor |

| RH8053GC021512 | Microprocessor |

| RH8053GC025512 | Microprocessor |

| RH8053GC029512 | Microprocessor |

| RH8053GC033512 | Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KP80526NY700128 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intel 功能描述: |

| KP80S 3601F200 | 制造商:STKE 功能描述: |

| KP80S 3602F100 | 制造商:STKE 功能描述: |

| KP80S1801F100 | 制造商:STK ELECTRONICS 功能描述: |

| KP80S2202J600 | 制造商:n/a 功能描述:AF322X600 5% |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。