- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360742 > ICS1531 Triple 8-bit MSPS A/D Converters with Line-Locked Clock Generator PDF資料下載

參數(shù)資料

| 型號: | ICS1531 |

| 英文描述: | Triple 8-bit MSPS A/D Converters with Line-Locked Clock Generator |

| 中文描述: | 三8位MSPS的的A / D轉(zhuǎn)換器與電源同步時鐘發(fā)生器 |

| 文件頁數(shù): | 29/76頁 |

| 文件大小: | 529K |

| 代理商: | ICS1531 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

Chapter 6

Register Set

ICS1531 Rev N 12/1/99

December, 1999

29

Copyright 1999, Integrated Circuit Systems, Inc.

All rights reserved.

ICS1531 Data Sheet - Preliminary

6.5.2

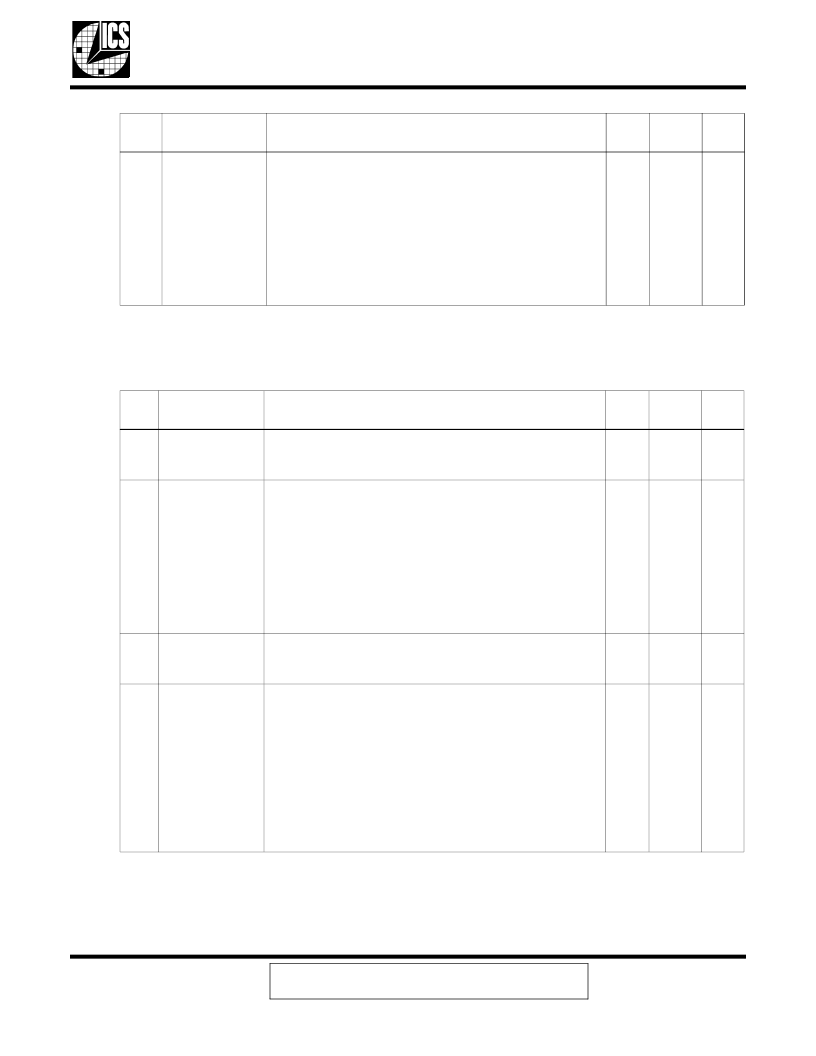

Register 01h: Loop Control Register

The Loop Control Register is used to control the pixel PLL.

00:0

PD_En

Phase/(Frequency) Detector Enable.

This bit is used to enable the Phase/Frequency Detector.

Typically, the signal for this bit is from the source of the VSYNC

signal to a display.

0 = The Phase/Frequency Detector is disabled temporarily

and ‘coasts’ (that is, it continues to be disabled) as long as

the signal from the PDEN pin is in an active state. (See

Reg 00:1).

1 = The Phase/Frequency Detector is enabled regardless

of the PDEN pin state. (This state overrides Reg 00:1.)

R/W

–

1

Table 6-4.

Loop Control Register

Bit

Bit Name

Bit Definition

Ac-

cess

Spec.

Func.

Re-

set

01:7-

01:6

Reserved

Reserved.

See

Section 6.1, “Reserved Bits”

.

These bits can be programmed to ‘0’.

–

–

0

01:5-

01:4

PSD [1-0]

Post-Scaler Divider [1-0].

These bits select the division value for the Post-Scaler

Divider (PSD).

By dividing the frequency output from the voltage-controlled

oscillator (VCO), the PSD can set the ratio of the VCO

frequency output to the pixel clock frequency as follows.

– 0 = Division is by 2, so the ratio is 2:1.

– 1 = Division is by 4, so the ratio is 4:1.

– 2 = Division is by 8, so the ratio is 8:1.

– 3 = Division is by 16, so the ratio is 16:1.

R/W

D-PLL

0

01:3

Reserved

Reserved.

See

Section 6.1, “Reserved Bits”

.

This bit can be programmed to ‘0’.

–

–

0

01:2-

01:0

PFD [2-0]

Phase/Frequency Detector (Gain) [2-0].

These bits select the gain (that is,

μ

A/2

π

rad) for the

Phase/Frequency Detector.

0 = PFD gain selected is 1

μ

A.

1 = PFD gain selected is 2

μ

A.

2 = PFD gain selected is 4

μ

A.

3 = PFD gain selected is 8

μ

A.

4 = PFD gain selected is 16

μ

A.

5 = PFD gain selected is 32

μ

A.

6 = PFD gain selected is 64

μ

A.

7 = PFD gain selected is 128

μ

A.

R/W

D-PLL

0

Table 6-3.

Input Control Register (

Continued

)

Bit

Bit Name

Bit Definition

Ac-

cess

Spec.

Func.

Re-

set

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS1560M-001 | Video/Graphics Clock Generator |

| ICS1560M-003 | Video/Graphics Clock Generator |

| ICS1560N-001 | Video/Graphics Clock Generator |

| ICS1560N-003 | Video/Graphics Clock Generator |

| ICS1561AM-706 | Video/Graphics Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS1532 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:110 MHZ TRIPLE 8-BIT ADC WITH CLOCK GENERATOR |

| ICS1560M-001 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560M-003 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560N-001 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

| ICS1560N-003 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video/Graphics Clock Generator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。