- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385403 > HT82J30R (Holtek Semiconductor Inc.) 16 Channel A/D MCU with SPI Interface PDF資料下載

參數(shù)資料

| 型號: | HT82J30R |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 16 Channel A/D MCU with SPI Interface |

| 中文描述: | 16通道A / D轉(zhuǎn)換,SPI接口單片機 |

| 文件頁數(shù): | 7/47頁 |

| 文件大?。?/td> | 312K |

| 代理商: | HT82J30R |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

HT82J30R/HT82J30A

Rev. 1.00

7

December 20, 2006

Program Memory

ROM

The program memory is used to store the program in-

structions which are to be executed. It also contains

data, table, and interrupt entries, and is organized into

4K 15bits,addressedbytheprogramcounterandtable

pointer.

Certain locations in the program memory are reserved

for special usage:

Location 000H

This area is reserved for program initialization. After

chip reset, the program always begins execution at lo-

cation 000H.

Location 004H

This area is reserved for the external interrupt service

program. If the INT0 input pin is activated, the inter-

rupt is enabled and the stack is not full, the program

begins execution at location 004H.

Location 008H

This area is reserved for the timer/event counter inter-

rupt service program. If a timer interrupt results from a

timer/event counter overflow, and if the interrupt is en-

abled and the stack is not full, the program begins exe-

cution at location 008H.

Location 00CH

This location is reserved for the A/D converter inter-

rupt service program. If the interrupt is activated,

when the A/D conversion is completed, if the interrupt

is enabledand the stack is not full, the programbegins

execution at this location.

Location 010H

Location010H is reservedfor when 8 bits of data have

been received or transmitted successfully from serial

interface A. When the related interrupts are enabled,

and the stack is not full, the program begins execution

at location 010H.

Location 014H

Location014H is reservedfor when 8 bits of data have

been received or transmitted successfully from serial

interface B. When the related interrupts are enabled,

and the stack is not full, the program begins execution

at location 014H.

Location 018H

This location is reserved for the external interrupt ser-

vice program. If the INT1 input pin is activated, the in-

terrupt is enabled and the stack is not full, the program

begins execution at this location.

Table location

Any location in the Program Memory space can be

used as a look-up table. The instructions TABRDC

[m]

(the current page, one page=256 words) and

TABRDL [m] (the last page) transfers the contents of

the lower-order byte to the specified data memory, and

the higher-order byte to the TBLH register. Only the

destination of the lower-order byte in the table is

well-defined, the other bits of the table word are trans-

ferred to the lower portion of TBLH. Any unused bits

are read as 0 . The Table Higher-order byte register,

TBLH, is read only. The table pointer, TBLP, is a

read/write register, which indicates the table location.

Beforeaccessingthetable,thelocationmustbeplaced

in TBLP. The TBLH register is read only and cannot be

restored. If the main routine and the ISR (Interrupt Ser-

vice Routine) both employ the table read instruction,

thecontentsofTBLHinthemainroutinearelikelytobe

changed by the table read instruction used in the ISR

and errors can occur. In other words, using the table

read instruction in the main routine and the ISR simul-

taneously should be avoided. However, if the table

@

& *

.

A " &

%

"

8

!

A

"

=

2

!

A

"

8 " #

" " 2 " B

"

8

!

A

"

6

!

A

"

6 1

!

A

"

=

2

!

A

"

(

7 !

A 2 ;

4

' & <

(

7 !

A 2 ;

4

' & <

C

5 C

/ C

C

C

/ C

5 C

. . . C

. . C

C

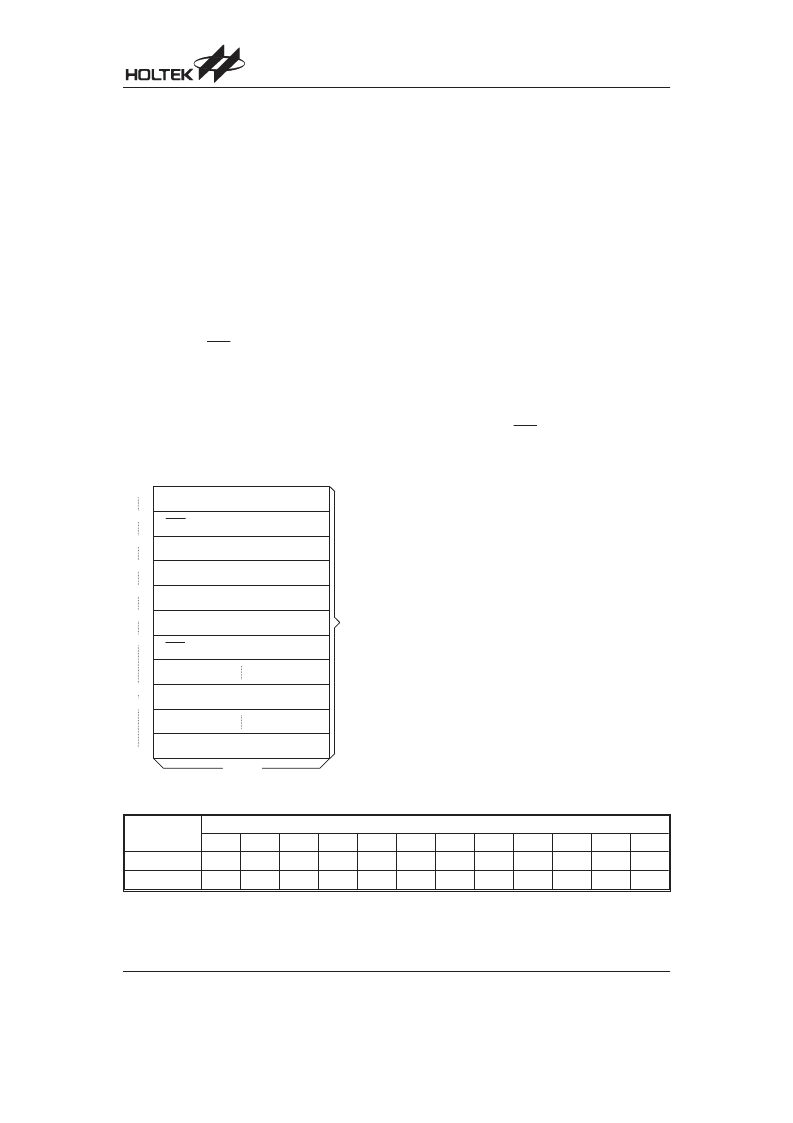

Program Memory

Instruction

Table Location

*11

*10

*9

*8

*7

*6

*5

*4

*3

*2

*1

*0

TABRDC [m]

P11

P10

P9

P8

@7

@6

@5

@4

@3

@2

@1

@0

TABRDL [m]

1

1

1

1

@7

@6

@5

@4

@3

@2

@1

@0

Table Location

Note: *11~*0: Table location bits

P11~P8: Current program counter bits

@7~@0: Table pointer bits

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82J927A | USB Gamepad |

| HT82J97E | USB Joystick Encoder 8-Bit OTP MCU |

| HT82J97E-20SOP-A | USB Joystick Encoder 8-Bit OTP MCU |

| HT82J97E-28SOP-A | USB Joystick Encoder 8-Bit OTP MCU |

| HT82K28 | Win98 Keyboard Encoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82J927A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Gamepad |

| HT82J97A_08 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Joystick Encoder 8-Bit MCU |

| HT82J97E | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Joystick Encoder 8-Bit OTP MCU |

| HT82J97E_08 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Joystick Encoder 8-Bit MCU |

| HT82J97E-20SOP-A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Joystick Encoder 8-Bit OTP MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。