- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385399 > HT46R221 (Holtek Semiconductor Inc.) 8-Bit A/D Type MCU PDF資料下載

參數(shù)資料

| 型號(hào): | HT46R221 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit A/D Type MCU |

| 中文描述: | 8位A / D型微控制器 |

| 文件頁(yè)數(shù): | 6/46頁(yè) |

| 文件大小: | 390K |

| 代理商: | HT46R221 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

HT46R22/HT46C22

Rev. 1.10

6

October 2, 2002

1

1

1

2

( -

9

:

;

& (

9

5 :

2

( -

9

<

:

;

& (

9

:

2

( -

9

<

:

;

& (

9

<

:

<

<

+

( %

! #

=

9

# ' ! + :

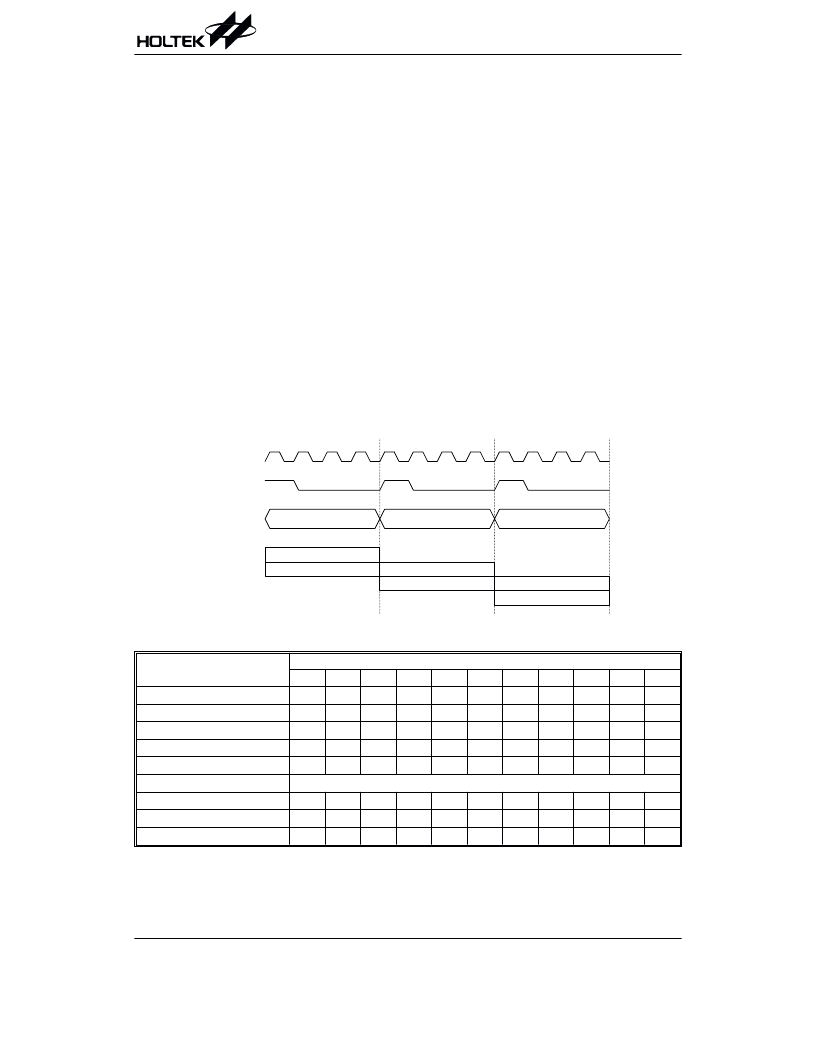

Execution flow

Functional Description

Execution flow

The system clock for the microcontroller is derived from

either a crystal or an RC oscillator. The system clock is

internally divided into four non-overlapping clocks. One

instruction cycle consists of four system clock cycles.

Instruction fetching and execution are pipelined in such

a way that a fetch takes an instruction cycle while de-

coding and execution takes the next instruction cycle.

However, the pipelining scheme causes each instruc-

tion to effectively execute in a cycle. If an instruction

changestheprogramcounter,twocyclesarerequiredto

complete the instruction.

Program counter

PC

The program counter (PC) controls the sequence in

which the instructions stored in program ROM are exe-

cuted and its contents specify full range of program

memory.

After accessing a program memory word to fetch an in-

struction code, the contents of the program counter are in-

cremented by 1. The program counter then points to the

memory word containing the next instruction code.

When executing a jump instruction, conditional skip ex-

ecution, loading PCL register, subroutine call, initial re-

set, internal interrupt, external interrupt or return from

subroutine, the PC manipulates the program transfer by

loading the address corresponding to each instruction.

The conditional skip is activated by instructions. Once

the condition is met, the next instruction, fetched during

the current instruction execution, is discarded and a

dummy cycle replaces it to get the proper instruction.

Otherwise proceed with the next instruction.

The lower byte of the program counter (PCL) is a read-

able and writeable register (06H). Moving data into the

PCL performs a short jump. The destination will be

within 256 locations.

When a control transfer takes place, an additional

dummy cycle is required.

Mode

Program Counter

*10

*9

*8

*7

*6

*5

*4

*3

*2

*1

*0

Initial Reset

0

0

0

0

0

0

0

0

0

0

0

External Interrupt

0

0

0

0

0

0

0

0

1

0

0

Timer/Event Counter Overflow

0

0

0

0

0

0

0

1

0

0

0

A/D Converter Interrupt

I

2

C BUS Interrupt

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

0

0

0

0

Skip

PC+2

Loading PCL

*10

*9

*8

@7

@6

@5

@4

@3

@2

@1

@0

Jump, Call Branch

#10

#9

#8

#7

#6

#5

#4

#3

#2

#1

#0

Return from Subroutine

S10

S9

S8

S7

S6

S5

S4

S3

S2

S1

S0

Program counter

Note: *10~*0: Program counter bits

S10~S0: Stack register bits

#10~#0: Instruction code bits

@7~@0: PCL bits

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT46C23 | A/D Type 8-Bit MCU |

| HT46C24 | A/D Type 8-Bit MCU |

| HT46R24 | A/D Type 8-Bit MCU |

| HT46C46 | Cost-Effective A/D Type 8-Bit MCU |

| HT46C47 | Cost-Effective A/D Type 8-Bit MCU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT46R23 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit OTP Microcontroller |

| HT46R232 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU |

| HT46R24 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU |

| HT46R24_06 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit MCU |

| HT46R32 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:A/D Type 8-Bit OTP MCU with OPA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。