- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385396 > HSP50215EVAL (Intersil Corporation) DSP Modulator Evaluation Board PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50215EVAL |

| 廠商: | Intersil Corporation |

| 英文描述: | DSP Modulator Evaluation Board |

| 中文描述: | DSP的調(diào)制器評(píng)估板 |

| 文件頁數(shù): | 9/21頁 |

| 文件大小: | 157K |

| 代理商: | HSP50215EVAL |

3-430

Re-Sampling NCO Application Issues

1. Common clocking of the PUC and PDC:

Note that at a board level, the HSP50214 (PDC) and

HSP50215 (DUC) sample rate NCO’s typically utilize

different clocks. The DUC circuitry is clocked at the master

clock, REFCLK, rate. The PDC output circuitry runs off the

decimated sample rate. If a common sample clock is used

for both parts, then synchronization can be achieved by

scaling and/or truncating the PDC frequency control word to

match the PUC frequency control word. Powers of 2 are

handled by simply truncating the PDC frequency control

word to match the bit width of the DUC frequency control

word. If the PDC decimation factor is not power of 2, then

errors will accumulate.

2. Improving the NCO Accuracy

The Re-Sampler NCO frequency can be adjusted to

maintain phase and frequency lock to a reference clock, if

more accuracy is required.

Interpolation Filter

The Interpolation filter provides sampling rate conversion

from the shaping filter output rate to the final output sample

rate. The nulls in the interpolation filter frequency response

align with the interpolation images of the shaping filter. The

impulse response of the Interpolation filter is shown in

Figures 9A through 9C for an interpolate by 16 filter (the

interpolation ratio, L, is equal to 16). The Interpolation filter

has a pipeline delay of 3 coarse input samples plus 3

REFCLK cycles.

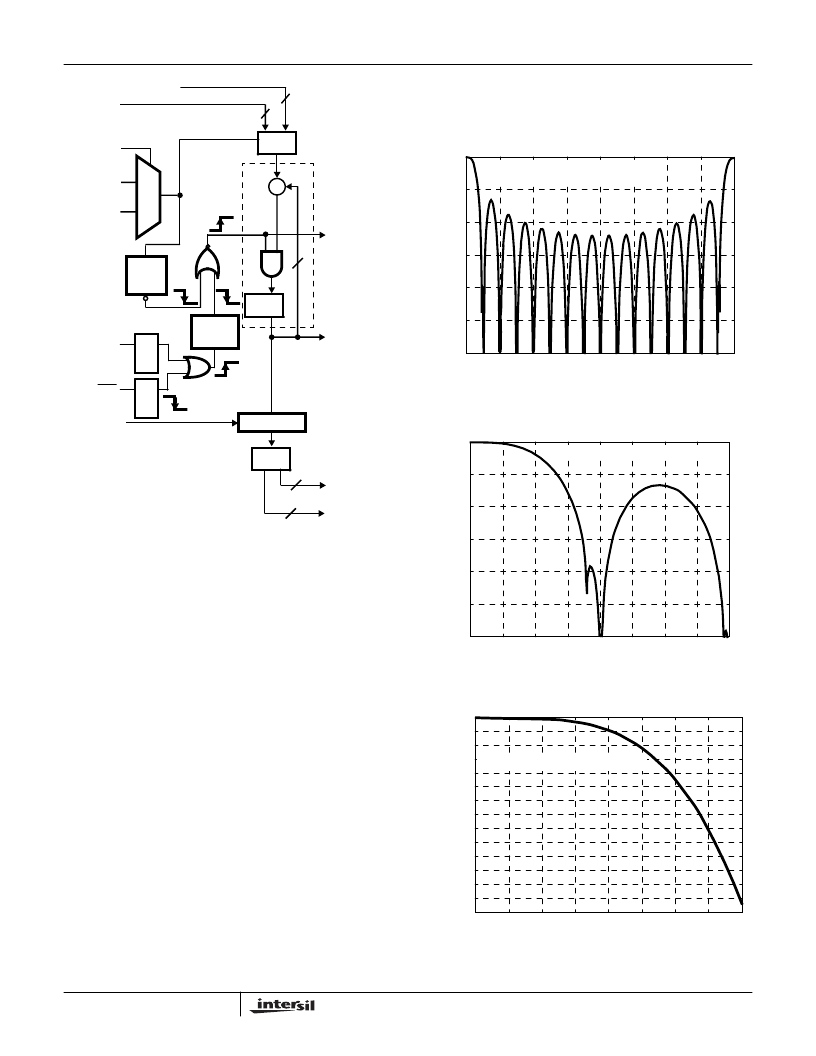

FIGURE 8. RE-SAMPLING NCO BLOCK DIAGRAM

12

30

32

SYNCIN

WR CW3

SAMPLE FREQUENCY

2

ZERO

SHIFTER

IP(1:0)

FINE

PHASE

COARSE

PHASE

SAMPCK

(MSB)

SYNCSEL

EN

ALL REGISTERS ARE

CLOCKED AT REFLCK

4, 3, OR 2

∑

REG

>

REG

>

REG

<

0

M

EnNCO

(CARRIER NCO)

ACC

START

EDGE

GEN

RESET

EDGE

GEN

WR CW21

RST

R

E

G

>

R

E

G

>

FIGURE 9A. INTERPOLATION FILTER IMPULSE RESPONSE

L = 16; FOUT = 4096

FIGURE 9B. INTERPOLATION FILTER IMPULSE RESPONSE

L = 16; FOUT = 4096

FIGURE 9C. INTERPOLATION FILTER IMPULSE RESPONSE

L = 16; FOUT = 4096

0

-20

-40

-60

-80

-100

-120

M

512

1024

1536

SAMPLE TIMES

2048

2560

3072

3584

4096

INTERPOLATION FILTER RESPONSE

0

-20

-40

-60

-80

-100

-120

M

64

128

192

SAMPLE TIMES

256

320

384

448

512

INTERPOLATION FILTER RESPONSE

0

-0.05

-0.1

-0.15

-0.2

-0.25

-0.3

-0.35

-0.4

-0.45

-0.5

-0.55

-0.6

-0.65

-0.7

M

8

16

24

SAMPLE TIMES

32

40

48

56

64

INTERPOLATION FILTER RESPONSE

HSP50215

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50215 | Digital UpConverter(數(shù)字上變頻器) |

| HSP50216 | Four-Channel Programmable Digital DownConverter(四通道可編程數(shù)字下變頻器) |

| HSP50307 | Burst QPSK Modulator(混合信號(hào)QPSK調(diào)制器) |

| HSP50415VI | CABLE ASSEMBLY; 75 OHM TNC MALE TO 75 OHM TNC MALE; 75 OHM, RG6A/U COAX |

| HSP50415EVAL1 | HSP50415EVAL1 Evaluation Kit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50215VC | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

| HSP50215VI | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

| HSP50216 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Four-Channel Programmable Digital Downconverter |

| HSP50216_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Four-Channel Programmable Digital DownConverter |

| HSP50216_07 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Four-Channel Programmable Digital Downconverter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。