- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385393 > HS1-80C85RH-Q (INTERSIL CORP) Radiation Hardened 8-Bit CMOS Microprocessor PDF資料下載

參數(shù)資料

| 型號: | HS1-80C85RH-Q |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Radiation Hardened 8-Bit CMOS Microprocessor |

| 中文描述: | 8-BIT, 2 MHz, MICROPROCESSOR, CDIP40 |

| 封裝: | SIDE BRAZED, METAL SEALED, CERAMIC, DIP-40 |

| 文件頁數(shù): | 9/16頁 |

| 文件大?。?/td> | 758K |

| 代理商: | HS1-80C85RH-Q |

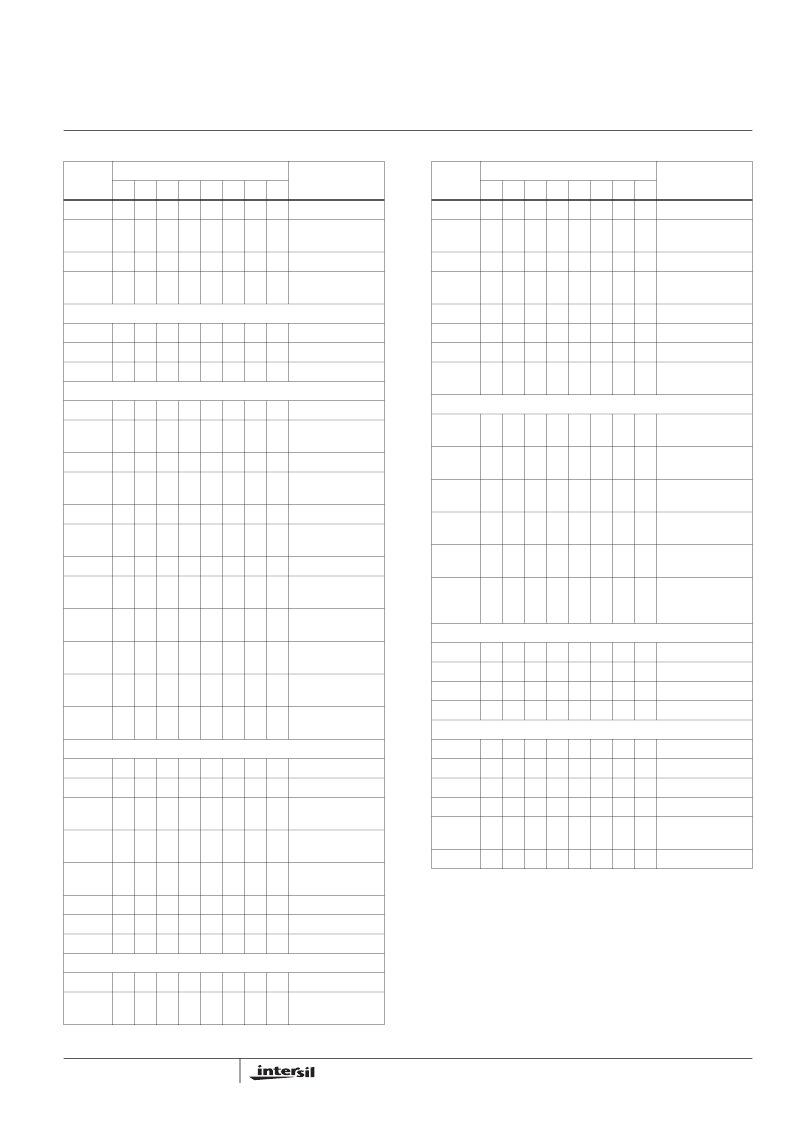

9

JM

1

1

1

1

1

0

1

0

Jump on minus

JPE

1

1

1

0

1

0

1

0

Jump on parity

even

JPO

1

1

1

0

0

0

1

0

Jump on parity odd

PCHL

1

1

1

0

1

0

0

1

H & L to program

counter

CALL

CALL

1

1

0

0

1

1

0

1

Call unconditional

CC

1

1

0

1

1

1

0

0

Call on carry

CNC

1

1

0

1

0

1

0

0

Call on no carry

LOGICAL

ANA r

1

0

1

0

0

S

S

S

And register with A

XRA r

1

0

1

0

1

S

S

S

Exclusive OR

register with A

ORA r

1

0

1

1

0

S

S

S

OR register with A

CMP r

1

0

1

1

1

S

S

S

Compare register

with A

ANA M

1

0

1

0

0

1

1

0

And memory with A

XRA M

1

0

1

0

1

1

1

0

Exclusive OR

memory with A

ORA M

1

0

1

1

0

1

1

0

OR memory with A

CMP M

1

0

1

1

1

1

1

0

Compare memory

with A

ANI

1

1

1

0

0

1

1

0

And immediate

with A

XRI

1

1

1

0

1

1

1

0

Exclusive OR

immediate with A

ORl

1

1

1

1

0

1

1

0

OR immediate

with A

CPl

1

1

1

1

1

1

1

0

Compare

immediate with A

ROTATE

RLC

0

0

0

0

0

1

1

1

Rotate A left

RRC

0

0

0

0

1

1

1

1

Rotate A right

RAL

0

0

0

1

0

1

1

1

Rotate A left

through carry

RAR

0

0

0

1

1

1

1

1

Rotate A right

through carry

INX H

0

0

1

0

0

0

1

1

Increment H & L

registers

DCX B

0

0

0

0

1

0

1

1

Decrement B & C

DCX D

0

0

0

1

1

0

1

1

Decrement D & E

DCX H

0

0

1

0

1

0

1

1

Decrement H & L

ADD

ADD r

1

0

0

0

0

S

S

S

Add register to A

ADC r

1

0

0

0

1

S

S

S

Add register to A

with carry

TABLE 4. INSTRUCTION SET SUMMARY (Continued)

MNE-

MONIC

INSTRUCTION CODE

OPERATIONS

DESCRIPTION

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

ADD M

1

0

C

0

0

1

1

0

Add memory to A

ADC M

1

0

0

0

1

1

1

0

Add memory to A

with carry

ADl

1

1

0

0

0

1

1

0

Add immediate to A

ACl

1

1

0

0

1

1

1

0

Add immediate to

A with carry

DAD B

0

0

0

0

1

0

0

1

Add B & C to H & L

DAD D

0

0

0

1

1

0

0

1

Add D & E to H & L

DAD H

0

0

1

0

1

0

0

1

Add H & L to H & L

DAD SP

0

0

1

1

1

0

0

1

Add stack pointer

to H & L

SUBTRACT

SUB r

1

0

0

1

0

S

S

S

Subtract register

from A

SBB r

1

0

0

1

1

S

S

S

Subtract register

from A with borrow

SUB M

1

0

0

1

0

1

1

0

Subtract memory

from A

SBB M

1

0

0

1

1

1

1

0

Subtract memory

from A with borrow

SUl

1

1

0

1

0

1

1

0

Subtract

immediate from A

SBl

1

1

0

1

1

1

1

0

Subtract

immediate from A

with borrow

SPECIALS

CMA

0

0

1

0

1

1

1

1

Complement A

STC

0

0

1

1

0

1

1

1

Set carry

CMC

0

0

1

1

1

1

1

1

Complement carry

DAA

0

0

1

0

0

1

1

1

Decimal adjust A

CONTROL

El

1

1

1

1

1

0

1

1

Enable Interrupts

DI

1

1

1

1

0

0

1

1

Disable Interrupt

NOP

0

0

0

0

0

0

0

0

No-operation

HLT

0

1

1

1

0

1

1

0

Halt

RIM

0

0

1

0

0

0

0

0

Read Interrupt

Mask

SlM

0

0

1

1

0

0

0

0

Set Interrupt Mask

NOTES:

4. DDS or SSS: B000, C001, D010, E011, H100, L101, Memory

110, A111

5. Two possible cycle times (6/12) indicate instruction cycles

dependent on condition flags.

All mnemonics copyrighted, Intel Corporation 1976

TABLE 4. INSTRUCTION SET SUMMARY (Continued)

MNE-

MONIC

INSTRUCTION CODE

OPERATIONS

DESCRIPTION

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

HS-80C85RH

相關PDF資料 |

PDF描述 |

|---|---|

| HS1-81C55RH-8 | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C55RH-Q | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C56RH-8 | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C56RH-Q | Radiation Hardened 256 x 8 CMOS RAM |

| HS1100 | RELATIVE HUMIDITY SENSOR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HS1-80C86RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 16-Bit CMOS Microprocessor |

| HS1-80C86RH/PROTO | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| HS1-80C86RH-8 | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 5MHZ 40PIN SBCDIP - Rail/Tube |

| HS1-80C86RH-Q | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 5MHZ 40PIN SBCDIP - Rail/Tube |

| HS18135 | 制造商:Microsemi Corporation 功能描述:POWER MODULE - DIODE - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。